VCK5000 Gen4x8 XDMA Vitis Platform¶

The Xilinx® Alveo® Versal® ACAP VCK5000 Data Center Development Kit is the industry’s first heterogeneous compute platform.

For more details on the VCK5000 card please see UG1428.

The VCK5000 card is supported by the Vitis® AI development environment which consists of optimized IP, tools, libraries, models, and example designs. Vitis AI has been designed with high efficiency and ease-of-use in mind, unleashing the full potential of AI acceleration on the VCK5000. Run Tensorflow, Pytorch, and Caffe models using Python or C++ APIs in minutes without any prior hardware knowledge about FPGAs or ACAPs.

Featuring the Xilinx® Versal ACAP XCVC1902 device, the VCK5000 is equipped with many of the common board-level features needed for design development, enabling the demonstration, evaluation, and development of applications, including:

PCIe attached acceleration.

Scalar processing of complex algorithms and decision making.

Vector processing for machine learning, video and image processing.

Signal processing of complex math, convolutions.

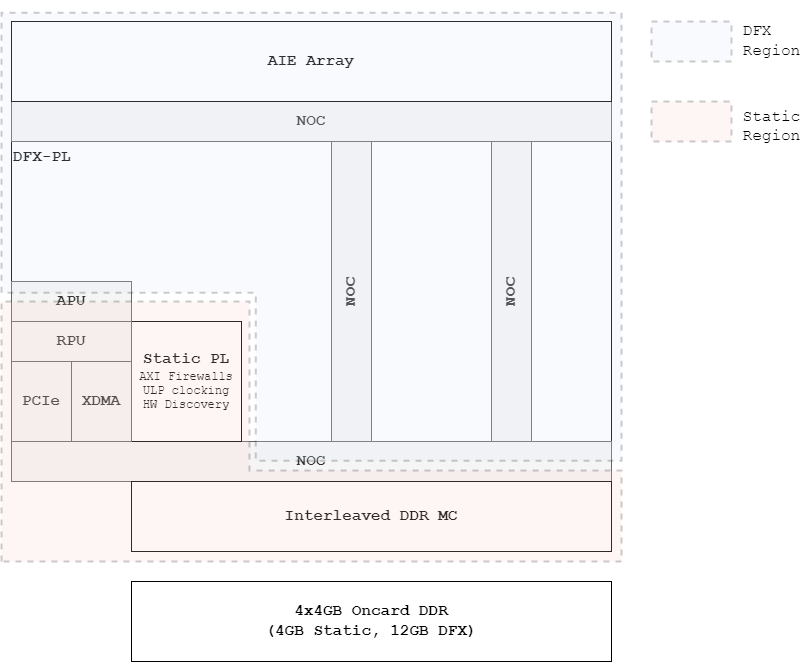

The division of Static and DFX regions for the Gen4x8 XDMA platform is shown below.

Figure: XDMA Platform Static and DFX Region¶

Static Region Components¶

PCIe Gen4x8 link for host to card connectivity

XDMA for application data movement between host memory and card memory

RPU for embedded card management including DFX download (XCLBIN), platform update, sensor reporting, etc.

APU OS loading for PS Kernel support

Installing a deployment platform on the cards instantiates the static region including the above components.

Important

Installation of the VCK5000 Gen4x8 XDMA deployment package requires additional steps compared to the prior VCK5000 Gen3x16 XDMA platform. Please review and follow all guidance on the VCK5000 migration page to ensure correct installation of this deployment package on the VCK5000 card.

DFX Region Components¶

PL region for HLS/RTL kernel Instantiation

APU User Space for PS Kernel Instantiation

12GB of on-card DDR-4 for user-kernel usage (RTL/HLS/PS)

AIE Array

Please see the following references for DFX kernel development utilizing the above DFX components:

AIE Tutorials for details on how to create a mixture of user kernels for the vck5000 platform including utilising the AIE kernel.

Vitis Examples for simple example DFX kernels, not specific to VCK5000

Platform Details¶

Platform name: xilinx-vck5000-gen4x8-xdma-base-2

Supported by: Vitis tools 2022.1, no support for other tools versions

Platform UUID: 04624343-B44B-B0A1-3CD4-8A411789FF20

Interface UUID: AE9AF7BC-A57D-DE8A-3BA8-A3F9262D78BB

Release Date: April 2022

Created by: 2022.1 tools

Supported XRT versions: 2022.1

Link speed: Up to 8 lane Gen4

Target card: VCK5000-AIE-ADK-P-G-ED

Feature Map¶

Feature |

Support |

|---|---|

DFX |

1-RP |

DMA |

XDMA PCIe Gen4x8, 2-channel, 512bit 250MHz datapath |

DDR |

12GB available to DFX |

PLRAM |

1x128KB |

DFX Clocking |

2x scalable clocks. Default 300MHz & 500MHz. 1 fixed 100MHz clock |

AIE |

yes |

GT |

GT Kernel Support |

Host Memory |

no |

Peer To Peer |

no |

For more details on each feature please see Platform Features

Static Region Floorplan and Resource Usage¶

As is shown above in Platform Static and DFX Region, the static region in the VCK5000 Gen4x8 XDMA mainly comprises the hardened PCIe interconnect, XDMA data mover, RPU processing subsystem and PL connectivity for the PL DFX region. The APU subsystem is loaded as part of the Static Region however it is available to run user applications in the form the PS Kernels.

The VCK5000 platform Static Region utilises mostly hard silicon IP and does not consume significant PL usage.

Type |

VC1902 Total |

Static Reserved |

% of Total |

DFX-Avail |

% of Total |

|---|---|---|---|---|---|

LUT |

900K |

22K |

2.4 |

878k |

97.6 |

FF |

1.8M |

44K |

2.4 |

1756K |

97.6 |

BRAM36 |

967 |

0 |

0 |

967 |

100 |

URAM |

463 |

0 |

0 |

463 |

100 |

DSP |

1968 |

0 |

0 |

1968 |

100 |

PL NMU |

28 |

2 |

7 |

26 |

93 |

PL NSU |

28 |

5 |

18 |

23 |

82 |

AIE Tiles |

400 |

0 |

0 |

400 |

100 |

All AIE tiles are available for application use. Please see https://www.xilinx.com/support/documentation/selection-guides/versal-ai-core-product-selection-guide.pdf for further information on available VC1902 device resources.

Card Thermal and Electrical Protections¶

The following consequent actions can occur when an electrical or thermal threshold is crossed.

Clock Shutdown

The DFX region clocks are stopped to immediately reduce power. The static region will remain operational. A hot reset is required to recover.

Card Shutdown

The power supplies are shutdown. Occurs was a fatal threshold is crossed to prevent damage to the card. A cold reboot will be required to recover.

Note

Dynamic clock throttling of the DFX region is not supported for this release.

The following electrical threshold limits are based on a 300W maximum electrical power design and assumes the 6-pin and 8-pin AUX power cables have been connected as per UG1531.

Sensor Description |

DFX Clock Shutdown Threshold |

Card Shutdown Threshold |

|---|---|---|

12V PEX power |

69W for >1s |

N/A |

12V AUX power |

231W for >1s |

N/A |

VCCINT current |

N/A |

60A per internal supply |

Note

VCCINT for this card is 0.78V and there are 6 internal VCCINT supplies.

Sensor Description |

Warning Threshold |

DFX Clock Shutdown Threshold |

Card Shutdown Threshold |

|---|---|---|---|

ACAP Temperature |

88°C |

100°C |

107°C |

VCCINT temperature |

100°C |

110°C |

125°C |

Xilinx Support

For additional support resources such as Answers, Documentation, Downloads, and Alerts, see the Xilinx Support pages. For additional assistance, post your question on the Xilinx Community Forums – Alveo Accelerator Card.

License

All software including scripts in this distribution are licensed under the Apache License, Version 2.0 (the “License”); you may not use this file except in compliance with the License.

You may obtain a copy of the License at http://www.apache.org/licenses/LICENSE-2.0

All images and documentation, including all debug and support documentation, are licensed under the Creative Commons (CC) Attribution 4.0 International License (the “CC-BY-4.0 License”); you may not use this file except in compliance with the CC-BY-4.0 License.

You may obtain a copy of the CC-BY-4.0 License at https://creativecommons.org/licenses/by/4.0/

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an “AS IS” BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.