2020.2 Vitis™ Getting Started TutorialSee 2020.1 Tutorials |

Vitis Flow 101 Tutorial¶

Welcome to the Vitis 101 tutorial. If you are looking to learn more about Vitis in order to get started with FPGA acceleration, you’ve come to the right place.

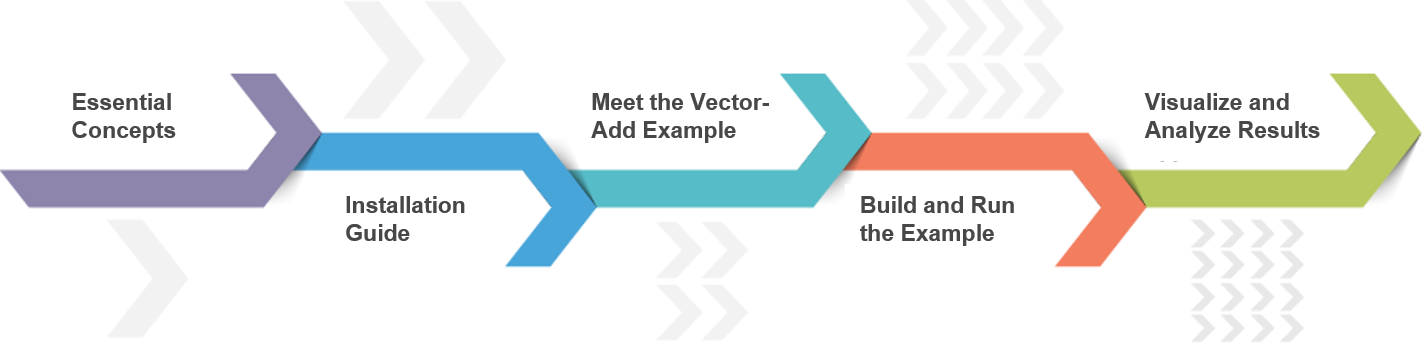

This tutorial is organized in 5 parts and is designed to walk you through all the key aspects of the Vitis flow.

Part 1 covers all the essential concepts of the Vitis FPGA acceleration flow in under 10 minutes

Part 2 guides you through the process of installing the Vitis tools, platforms and runtime library.

Part 3 explains the source code of vector-add example used in the rest of the tutorial

Part 4 describes the commands required to compile, link and run the example on your acceleration card

Part 5 gives an overview of Vitis Analyzer and shows how to open and analyze reports

Vitis provides a unified flow for developing FPGA accelerated application targeted to either data-center or embedded platforms. This tutorial provides instructions for building and running on both ZCU102 and Alveo U200 cards. These instructions can be easily adapted to other Xilinx cards.

NOTE: This tutorial requires Vitis 2020.2 or later to run.

Click here to start the Vitis Flow 101 Tutorial

Copyright© 2020 Xilinx