RTL カーネル (rtc_gen) の作成¶

Vitis/Vivado RTL Kernel Wizard を使用すると、簡単に RTL ベースのカーネルを作成および開発して、ほかの HLS C または Vitis ビジョン ライブラリ ベースのカーネルを Vitis とシームレスに統合できます。このチュートリアルでは、rtc_gen カーネルを作成する詳細な手順を示します。チュートリアルのターゲット プラットフォームには、Alveo U200 を使用します。

最上位デザインの仕様の決定¶

rtc_gen カーネルは、フォント ライブラリをグローバル メモリからオンチップ SRAM に読み出し、AXI-Stream ポートを介してクロック画像を出力する必要があります。フォント ライブラリの読み出しは 1 回限りのジョブであり、通常の作業でグローバル メモリ帯域幅の要件はありません。このため、フォント読み出しポートに 32 ビット (データ バス) の AXI4 マスター インターフェイスを使用して、リソースを節約します。ダウンストリーム処理のパイプラインでは、XF_NPP8 形式 (毎クロック サイクルで 8 ピクセル処理) を使用するため、AXI-Stream 幅を 64 ビットに選択し、AXI-Stream トランザクションごとに 8 ピクセルを転送できるようにします。制御レジスタには、XRT と互換性のある AXI スレーブ インターフェイスを使用するので、標準の OpenCL API を使用してカーネルをプログラムおよび制御できます。

このため、rtc_gen カーネルの最上位デザイン仕様を次のように一般化します。

バス インターフェイス

制御用の AXI4-Lite スレーブ インターフェイス

データ幅 32 ビット、アドレス幅 64 ビットのフォント データの読み込み用の AXI4-Lite マスター インターフェイス

データ幅 64 ビットのクロック桁画像出力用の AXI-Stream マスター インターフェイス

制御レジスタ

| 番号 | 引数 | 幅 | 説明 |

|---|---|---|---|

| 0 | work_mode | 1 | [0]: カーネルの動作モードを決定します。 0 - AXI 読み出しマスターを介してグローバル メモリからオンチップ SRAM までのフォントを読み込みます。 1 - AXI-Stream マスターを介して RTC 桁の図を出力します。 |

| 1 | cs_count | 32 | [21:0]: センチ秒カウンター。たとえば、システム クロックが 200 MHz の場合、cs_count は 2,000,000 に設定する必要があります。 |

| 2 | time_format | 1 | [0]: センチ秒が出力桁の画像に含まれているかどうかを確認します。 0 - センチ秒の出力をディスエーブルにします。 1 - センチ秒の出力をディスエーブルにします。 |

| 3 | time_set_val | 32 | 内部フリーランニング クロックの時間値を設定します。 [31:24] - 時間 [23:16] - 分 [15:8] - 秒 [7:0] - センチ秒 |

| 4 | time_set_en | 1 | [0]: このビットに 1 を書き込むと、time_set_value が内部フリーランニング クロックに読み込まれます。 |

| 5 | time_val | 32 | 内部リアルタイム クロック時間値の読み取り専用レジスタ: [31:24] - 時間 [23:16] - 分 [15:8] - 秒 [7:0] - センチ秒 |

| 6 | read_addr | 64 | AXI マスター ポインター。これは、フォント ライブラリ用の FPGA デバイス バッファー アドレスです。 |

RTL Kernel Wizard を使用したカーネル フレームの作成¶

では、RTL Kernel Wizard を使用して rtc_gen カーネルのフレームを作成します。Vivado からウィザードを起動します。RTL カーネルおよび RTL Kernel Wizard の詳細なユーザー ガイドは、Vitis アプリケーション アクセラレーション開発フローの資料を参照してください。

git repo の ./rtc_gen ディレクトリに移動し、vivado_project という名前のディレクトリを作成してから、このディレクトリを入力します。

cd ./rtc_gen

mkdir vivado_project

cd ./vivado_project

vivado &

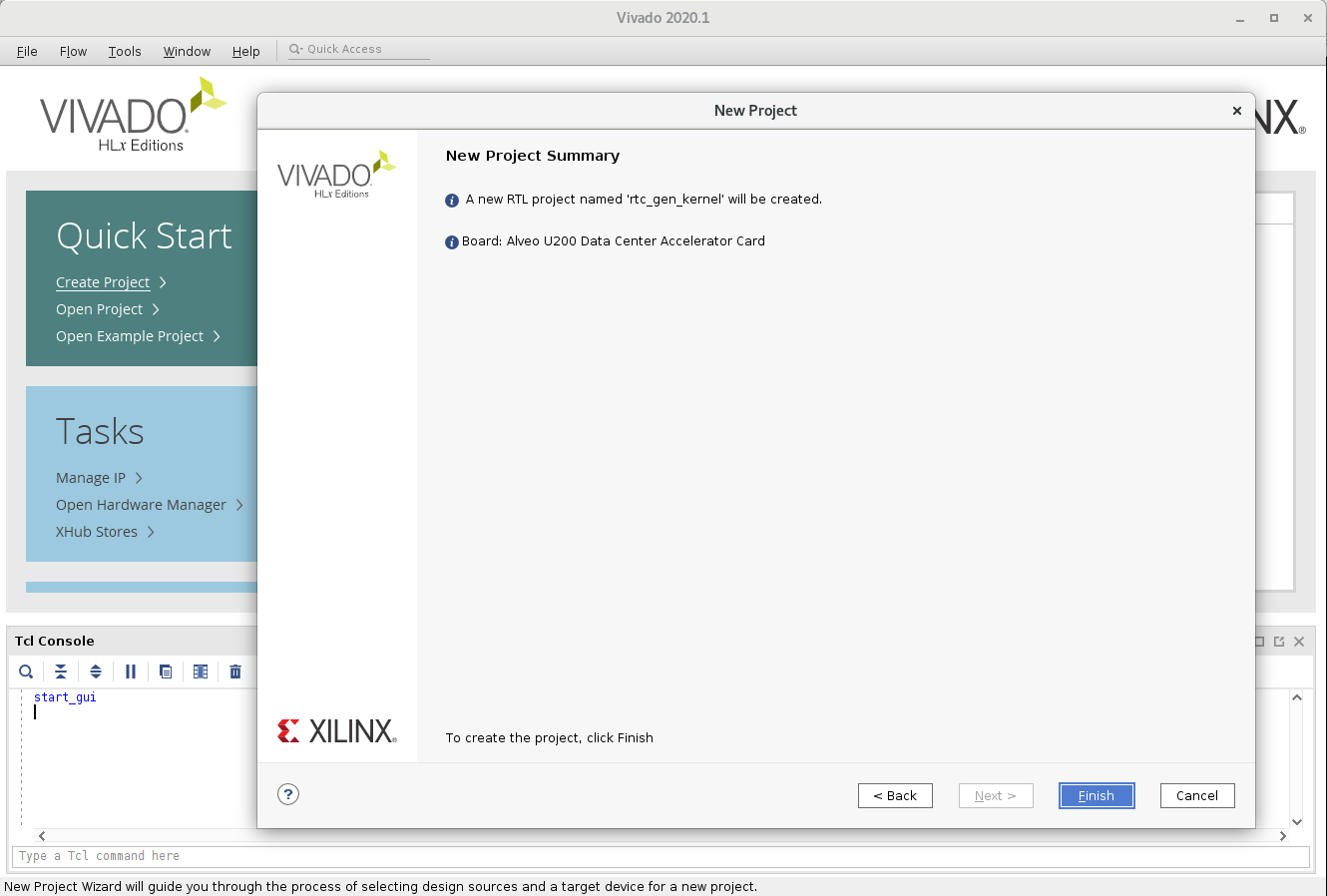

先ほど作成した vivado_project ディレクトリに、rtc_gen_kernel という名前の新しい RTL プロジェクトを作成します。パーツを選択するページで、*[Alveo U200 Data Center Accelerator Card] を選択します。

プロジェクトが作成されたら、Flow Navigator で [IP Catalog] をクリックし、IP カタログの検索ボックスに「RTL Kernel」と入力し、RTL Kernel Wizard をダブルクリックしてウィザードを起動します。

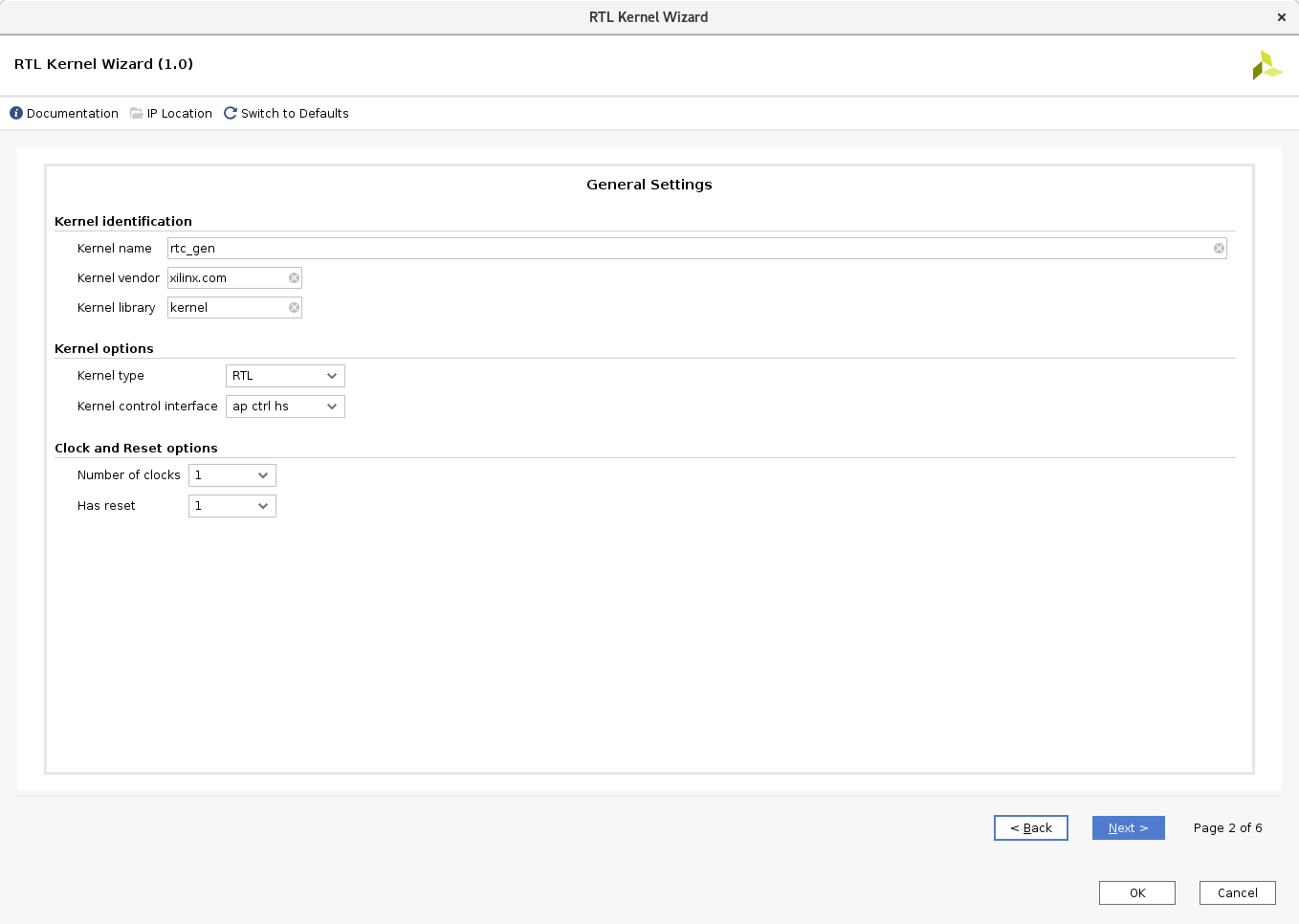

次の図のように、RTL Kernel Wizard の [General Settings] タブでカーネル名を rtc_gen に設定し、カーネル ベンダーを xilinx.com に設定し、[has reset] オプションの値を 1 に変更します。

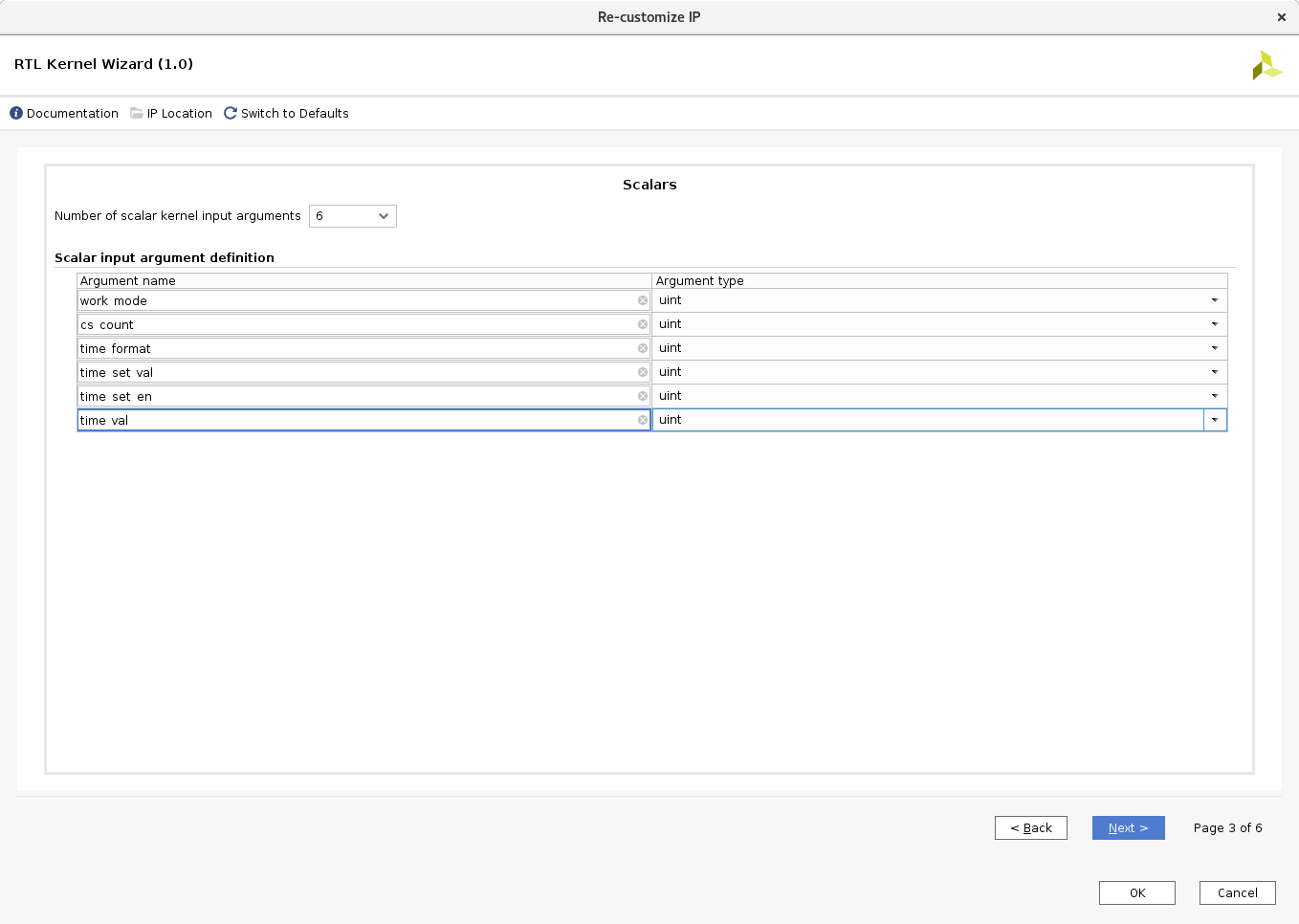

[Scalars] タブでカーネル引数をデザイン仕様として設定します。次の図の [Control Register] の表を参照してください。read_addr レジスタは、AXI マスター ポインターのようにスカラー引数とは見なされないため、このタブで設定する必要はありません。ここでは引数の型として uint を使用していますが、これらのビットはすべて使用されない可能性があります。

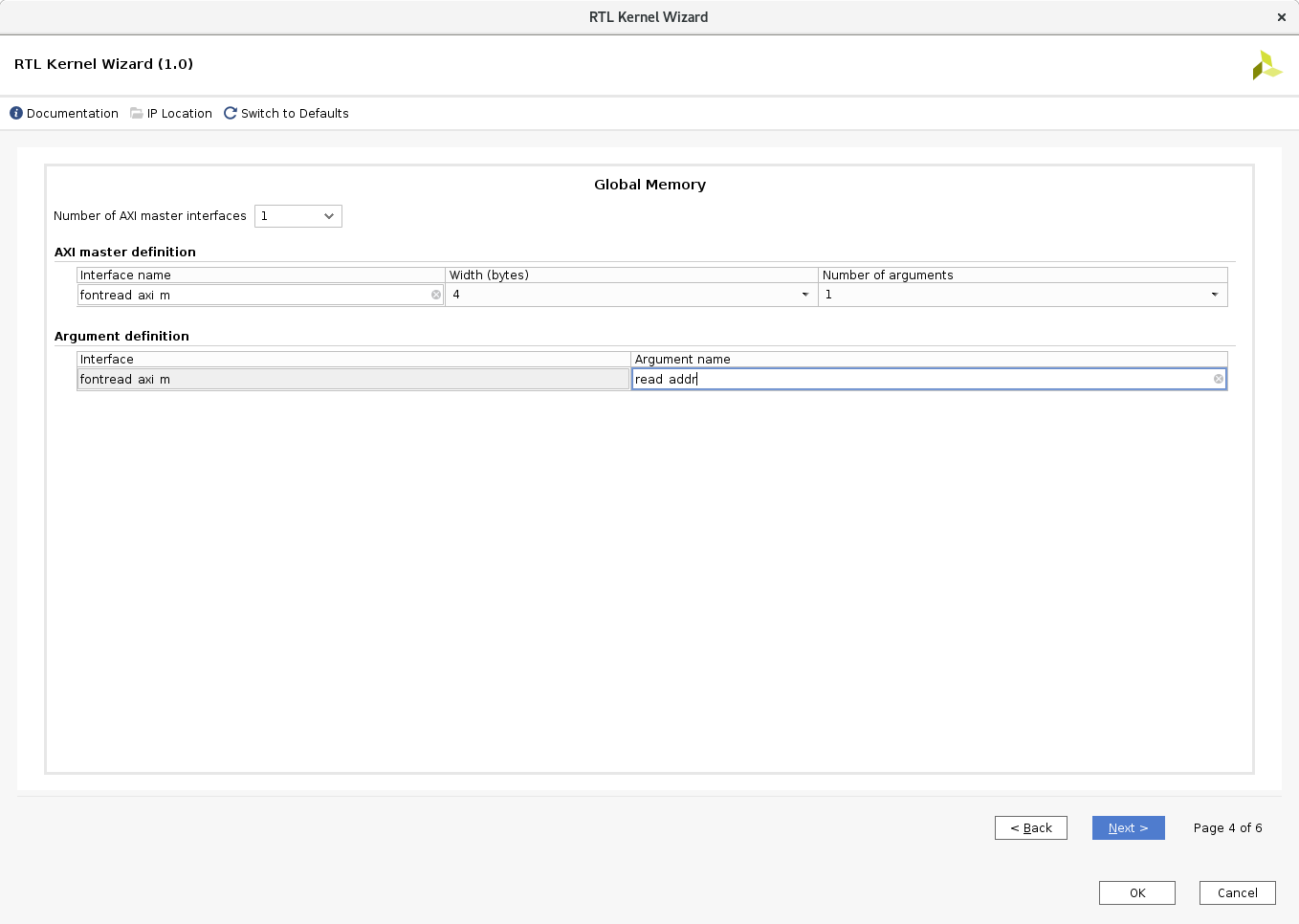

[Global Memory] タブでデザイン仕様に従って AXI マスター インターフェイス パラメーターを設定します。AXI マスター インターフェイスに fontread_axi_m という名前を付け、幅を 4 バイト (32 ビット) に変更し、関連する引数名を read_addr に設定します。次のスナップショットを参照してください。

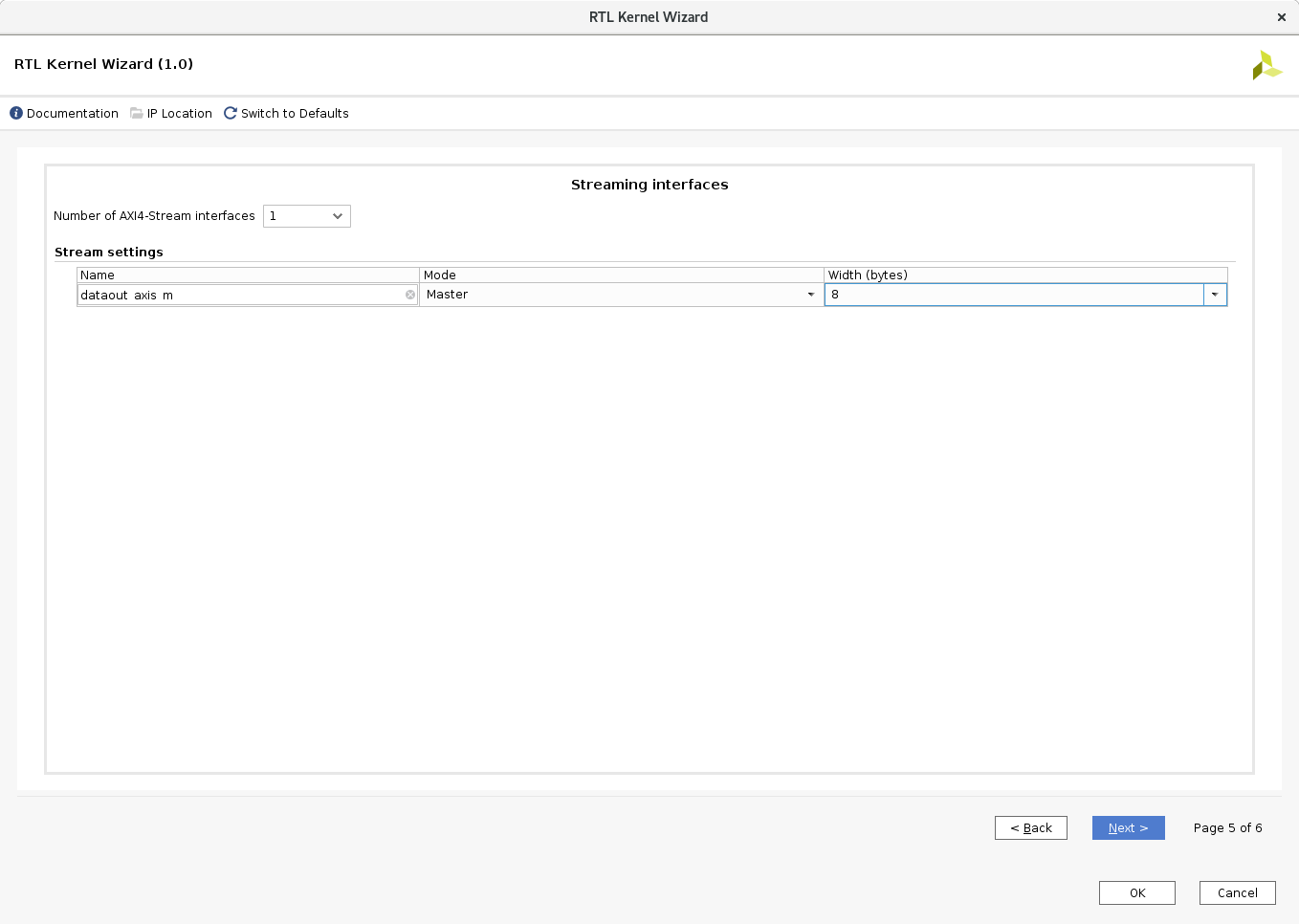

[Streaming Interfaces] タブで AXI4-Sttream インターフェイスの数を 1 に設定し、dataout_axis_m という名前にし、モードを [Master] に設定し、幅を 8 バイト (64 ビット) に設定します。次のスナップショットを参照してください。

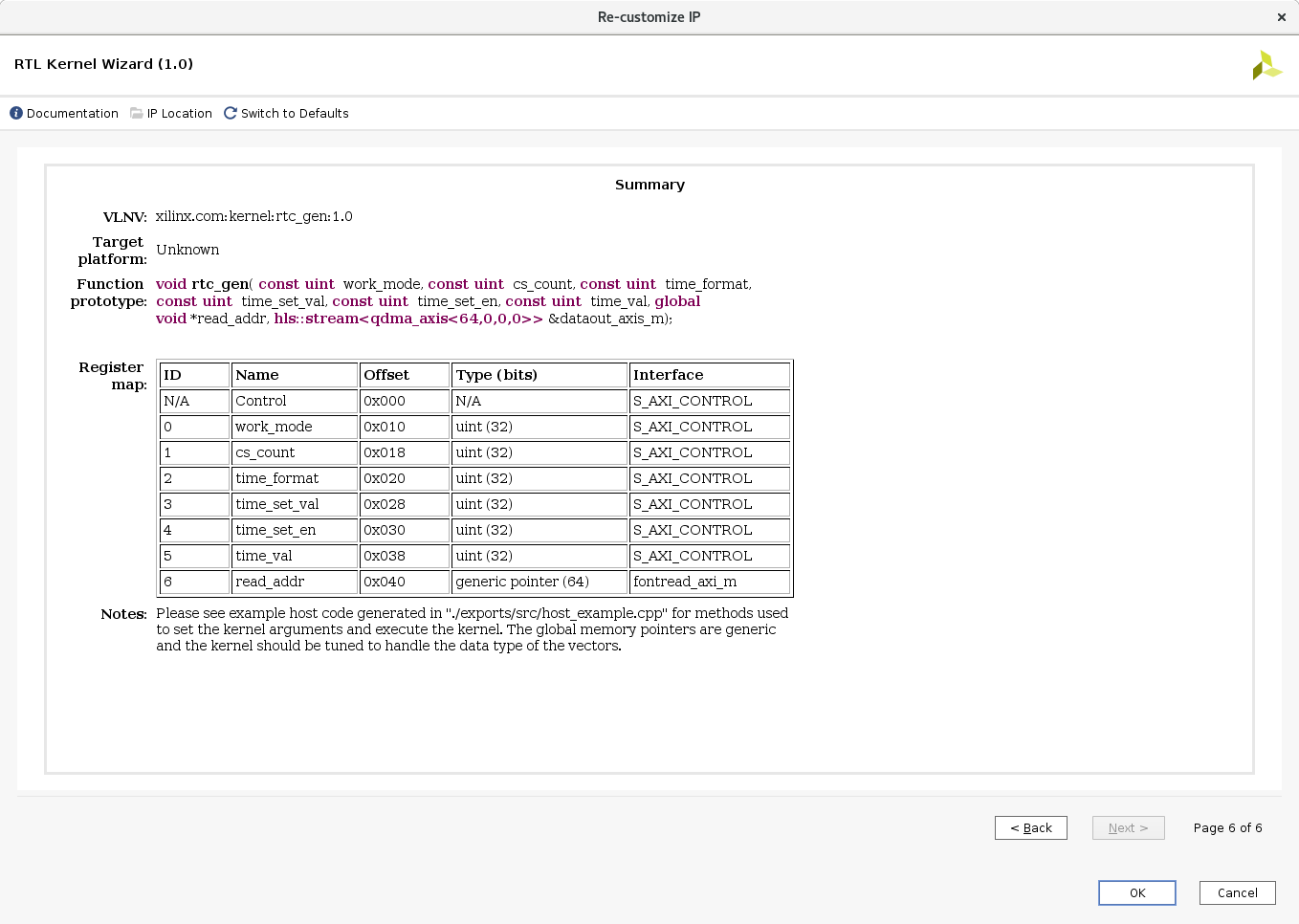

最後にウィザードのサマリ ページを確認し、[OK] ボタンをクリックして RTL カーネルの最上位フレームワークを生成します。

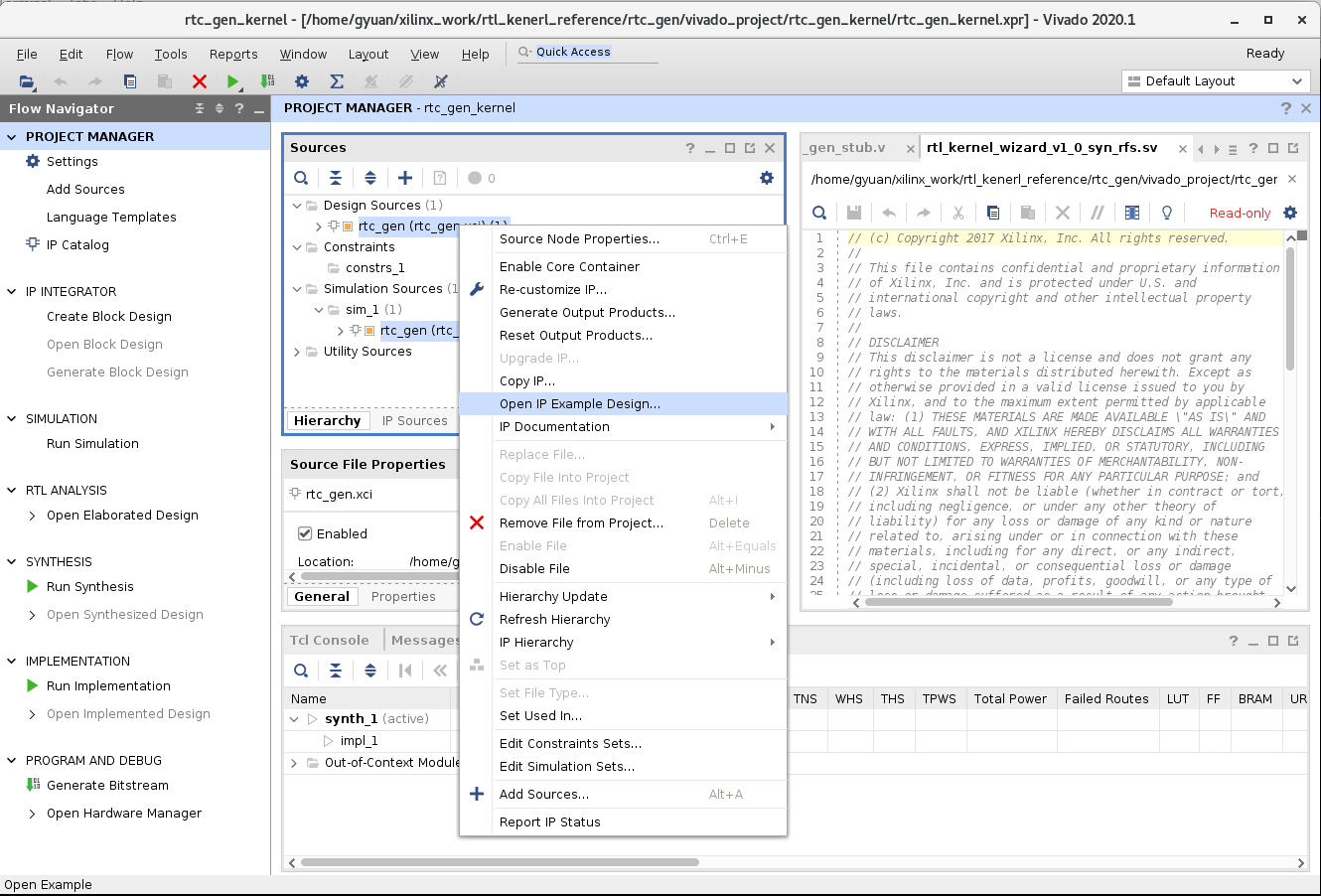

次の [Generate Output Products] ポップアップ ウィンドウでは、[Skip] ボタンをクリックしてウィンドウを閉じます。これで、[Sources] ビューの [Design Sources] グループに rtc_gen.xci ファイルが表示されるよになります。rtc_gen.xci ファイルを右クリックし、[Open IP Example Design] をクリックします。

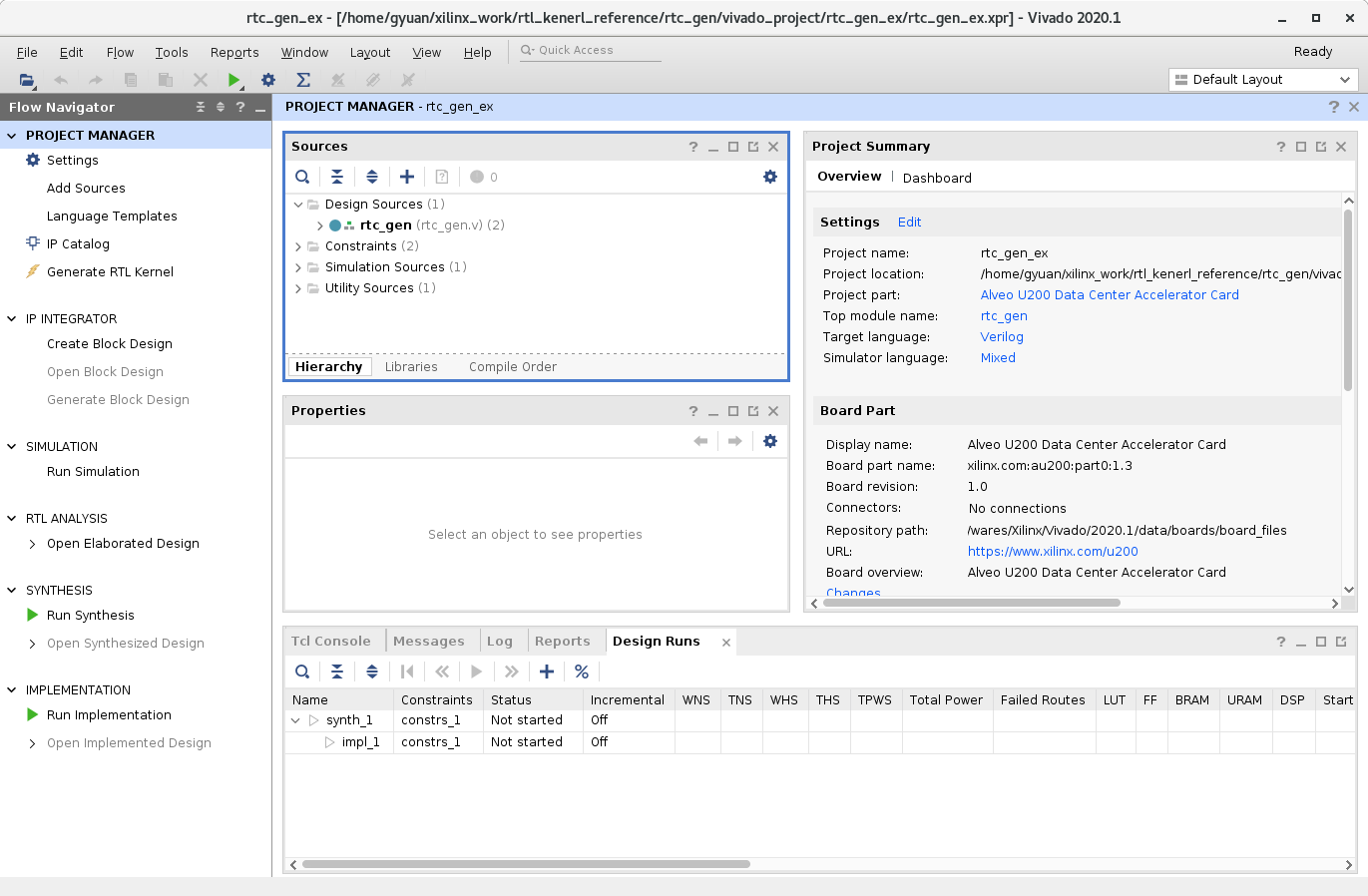

[Open IP Example Design] ポップアップ ウィンドウで [OK] ボタンをクリックすると、rtc_gen_ex という名前の別のプロジェクトが ./vavado_project ディレクトリに作成され、別の Vivado セッションで自動的に開きます。主な作業プロジェクトとして rtc_gen_ex を使用し、rtc_gen カーネル開発を終了します。

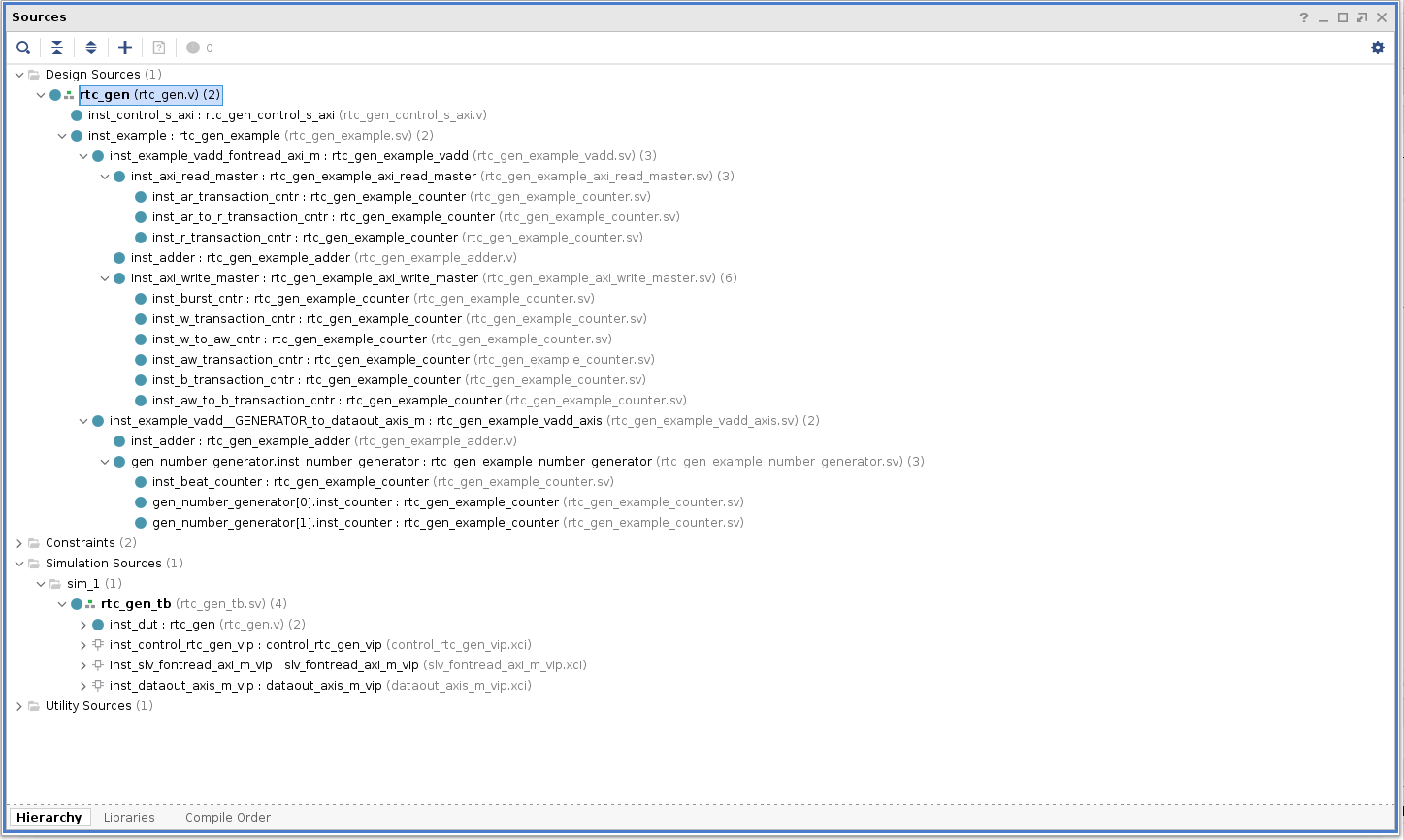

rtc_gen_ex プロジェクトには、自動的に生成された Verilog/SystemVerilog ソース コード ファイルがいくつか表示されます。

rtc_gen_control_s_axi.v

rtc_gen_example_adder.v

rtc_gen_example_axi_read_master.sv

rtc_gen_example_axi_write_master.sv

rtc_gen_example_counter.sv

rtc_gen_example_number_generator.sv

rtc_gen_example.sv

rtc_gen_example_vadd_axis.sv

rtc_gen_example_vadd.sv

rtc_gen_tb.sv

rtc_gen.v

[Sources] ビューの [Hierarchy] タブでは、HDL ファイル階層を確認できます。これでカーネル フレームワークの作成は終了です。

rtc_gen カーネルの開発¶

rtc_gen カーネルでは、次の生成済み RTL ファイルを使用します。

rtc_gen_control_s_axi.v

上位レベルのシステムおよび XRT への AXI Lite スレーブ インターフェイスで、すべてのカーネル引数とカーネル制御信号 (ap_start、ap_done、ap_idle、ap_ready) が含まれます。このモジュールを少し変更して、読み取り専用レジスタの time_val を実現します。

rtc_gen_example_axi_read_master.sv

単純な AXI Lite 読み出しマスターで、カーネルから直接呼び出すことができます。4 つの制御信号を使用してマスターをトリガーし、データ読み出しタスクを完了します。

ctrl_start: マスター ステート マシンを開始する単一のサイクル パルス

ctrl_done: AXI 読み出しタスクの終了を示す単一のサイクル パルス

ctrl_addr_offset: AXI 読み出し操作のベース アドレス。この信号は、カーネル引数 read_addr を使用すると駆動できます。

ctrl_xfer_size_in_bytes: AXI バスから読み出されるバイト数。

マスターの例もデータ転送の読み出しに AXI-Stream ポートを使用します。このポートは、データ パイプラインのように FIFO に簡単に接続できます。

rtc_gen_example_counter.sv

AXI 読み出しマスターの例のサブモジュール。

rtc_gen.v すべてのサブモジュールをインスタンシエートする最上位のカーネル ラッパーの例です。このモジュールを変更して、rtc_gen カーネルを構築します。

rt_gen_tb.sv ザイリンクス AXI Verification IP を使用したテストベンチの例です。このテストベンチを変更して rtc_gen カーネルをテストできます。

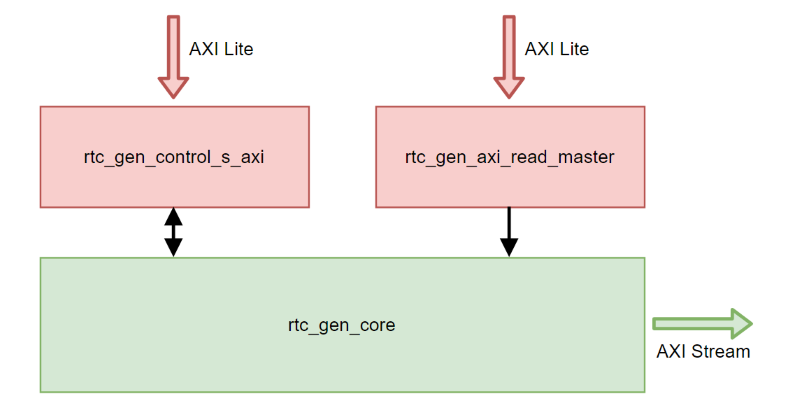

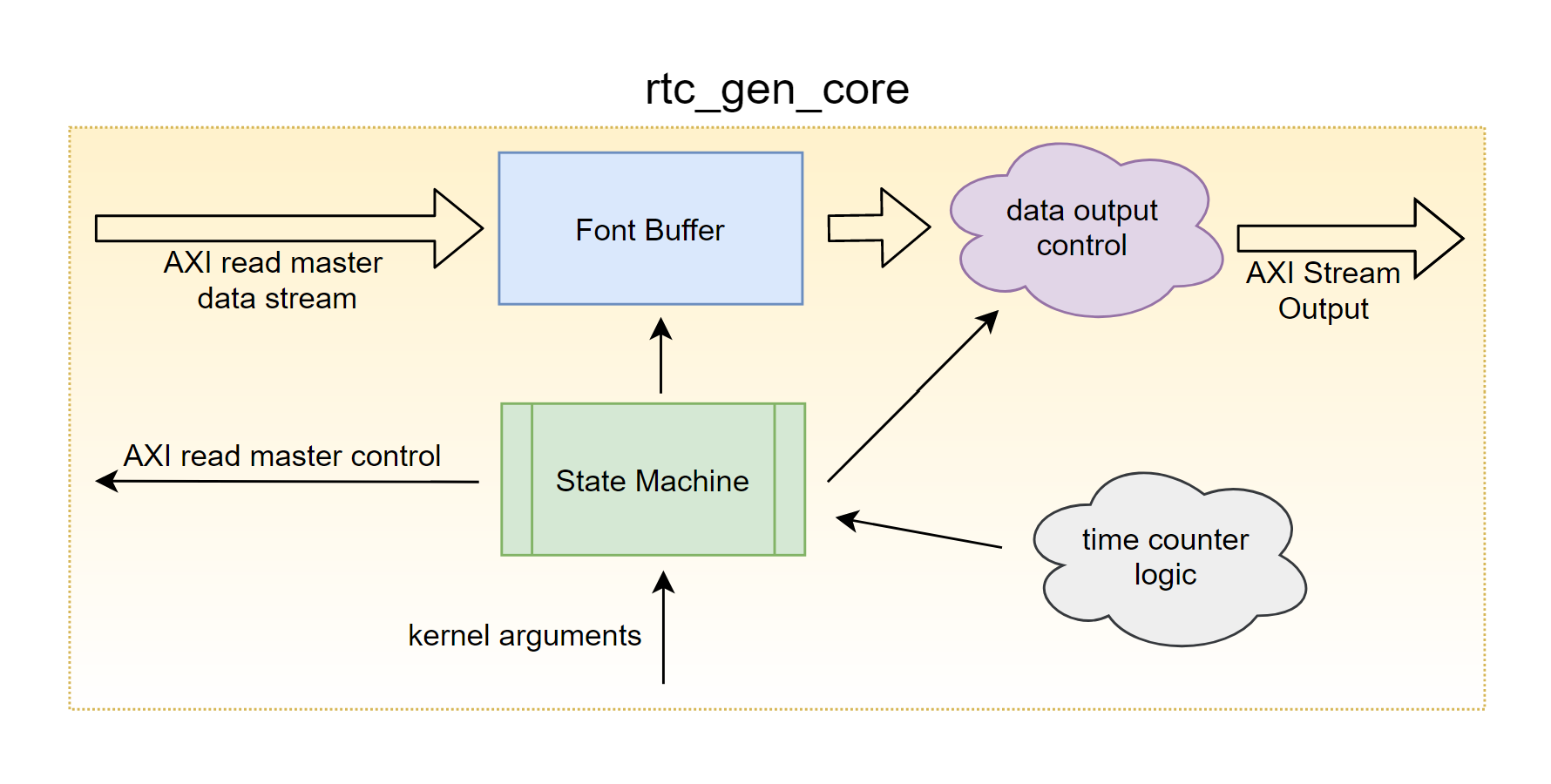

AXI 読み出しマスターの接続の詳細は、これらの 5 つのファイルに加えて、rtc_gen_example_vadd.sv を参照することもできます。AXI-Stream ポートの場合は単純なので、参照用の例は必要ありません。rtc_gen カーネルの場合、Verilog ファイルの rtc_gen_core.v が作成され、カーネルのコア ファンクションを完了します。rtc_gen_core のファンクション図を次に示します。

コアのソース コード ディレクトリをクリーンにするため、生成した RTL ファイル、新しく作成した RTL ファイル、または変更した RTL ファイルを ~/rtc_gen/src ディレクトリにすべて配置します。これらのソース コード ファイルのディレクトリを確認してください。SPSR.v は、FPGA BlockRAM に合成できるパラメーター変更可能な SRAM テンプレートです。

./rtc_gen/src/rtc_gen_control_s_axi.v

./rtc_gen/src/rtc_gen_core.v

./rtc_gen/src/rtc_gen_example_axi_read_master.sv

./rtc_gen/src/rtc_gen_example_counter.sv

./rtc_gen/src/rtc_gen_tb.sv

./rtc_gen/src/rtc_gen.v

./rtc_gen/src/SPSR.v

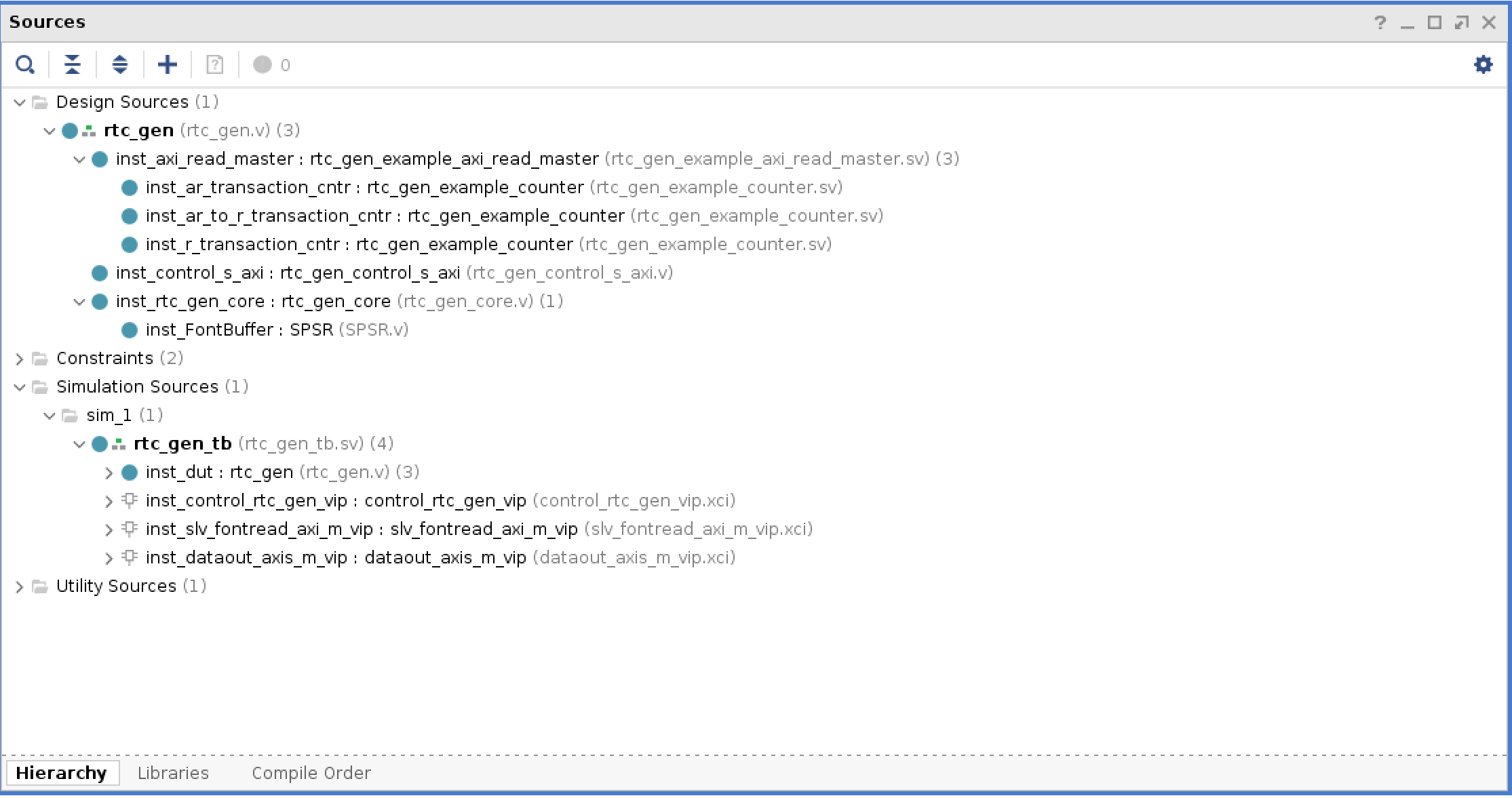

次に、Vivado の rtc_gen_ex プロジェクトから既存のすべての Verilog/SystemVerilog ソース コード (IP グループ内のものを除く) を削除し、./rtc_gen/src のファイルをプロジェクト ([Simulation-Only Sources] の場合は rtc_gen_tb.sv、[Design Sources] の場合はその他のファイル) を追加します。デザイン階層は次の図のようになります。rtc_gen カーネルのコーディングはこれで終了です。

これで、標準的な Vivado デザイン手法を使用して、デザインをシミュレーションし、通常の RTL デザイン フローを実行できるようになりました。提供されるテキスト形式のフォント ライブラリ ファイル (./rtc_gen ディレクトリの font_sim_data.txt) を rtc_gen_tb.sv テストベンチで読み込むと、シミュレーションできます。シミュレーション実行の場合は、これを ./rtc_gen/vivado_project/rtc_gen_ex/rtc_gen_ex.sim/sim_1/behav/xsim/ にコピーします。

RTL カーネルのパッケージ¶

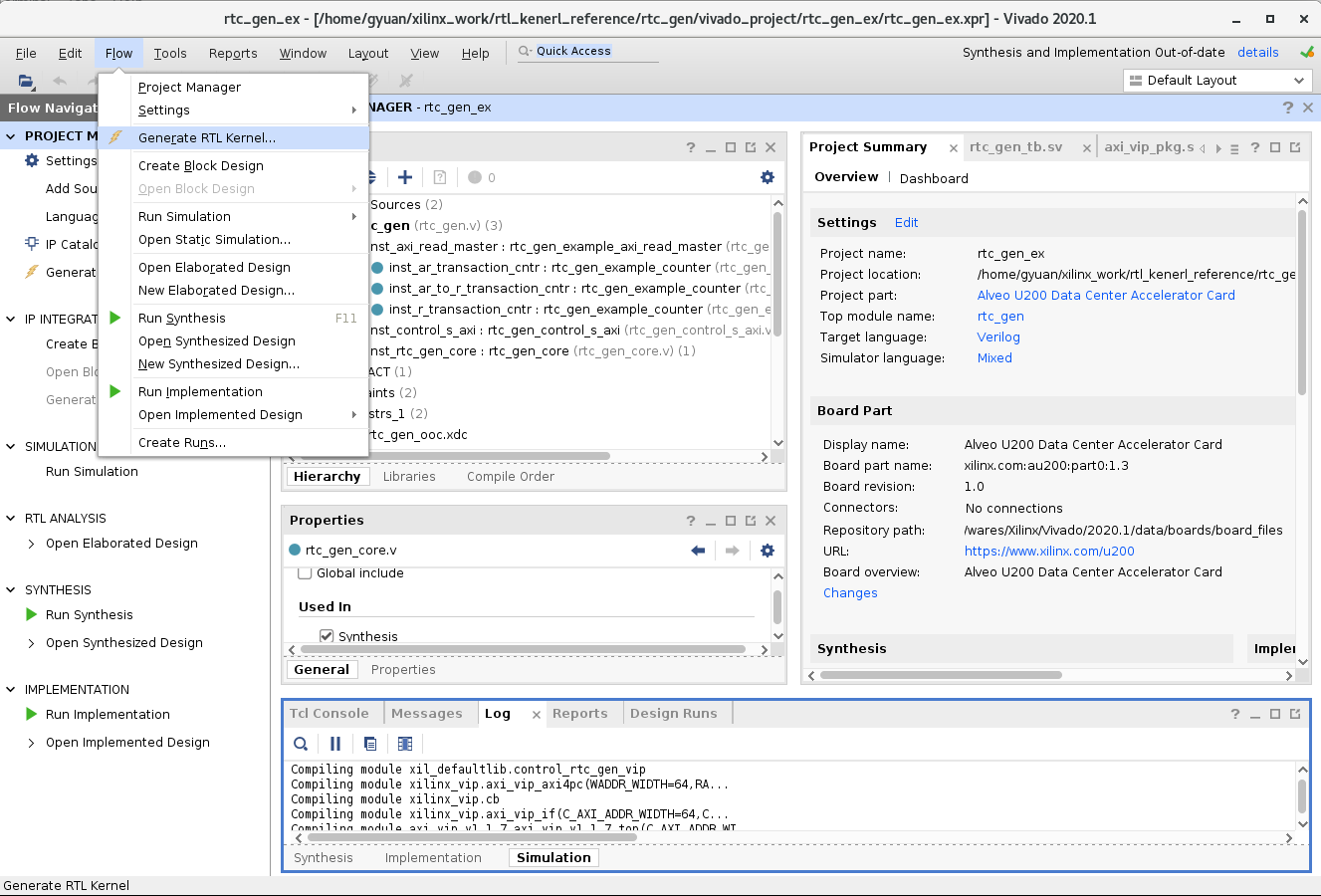

デザインに問題がないことを確認したら、[Flow] メニューから [Generate RTL Kernel] をクリックし、ポップアップ ウィンドウで [Sources-only kernel] を選択し、[OK] ボタンをクリックしたら、RTL カーネル (rtc_gen) の作成は終了です。

生成されたカーネル ファイルは ./rtc_gen/vivado_project/rtc_gen_ex/rtc_gen.xo で、ダウンストリームの Vitis 統合フローで使用できます。Vivado の [Tcl Console] ビューからは、Vivado が実際に次のコマンド ラインを使用してカーネルのパッケージを終了したことがわかります。

package_xo -xo_path ./rtc_gen/vivado_project/rtc_gen_ex/exports/rtc_gen.xo \

-kernel_name rtc_gen \

-ip_directory ./rtc_gen/vivado_project/rtc_gen_ex/rtc_gen \

-kernel_xml ./rtc_gen/vivado_project/rtc_gen_ex/imports/kernel.xml

./rtc_gen/vivado_project/rtc_gen_ex/rtc_gen は rtc_gen IP のフォルダーで、./rtc_gen/vivado_project/rtc_gen_ex/imports/kernel.xml はカーネル記述ファイルです。これらをスタンドアロンのディレクトリにコピーし、上記のコマンド ラインを使うと、カーネルをパッケージできます。これは、./hw/rtc_gen_ip ディレクトリと ./hw/rtc_gen_kernel.xml ファイルの元にもなります。

Copyright© 2020 Xilinx