Vitis ハードウェア アクセラレーションxilinx.com の Vitis™ 開発環境を参照 |

このセクションの内容

C 合成を実行してデザインの RTL 記述を作成し、使用されるコンパイラ ヒント (プラグマ) について説明します。

Vitis HLS C 合成の実行¶

前のフェーズの C シミュレーションでは、コードの実行は純粋に C ベースでした。ストリームに対して特定のライブラリが使用されるものの、RTL は関与していませんでした。

C 合成では、HLS コンパイラに渡されるヒント (プラグマまたは指示子と呼ばれる) に基づいて最上位関数 tsp が解析およびコンパイルされます。 演算がスケジューリングされてハードウェア コンストラクトにマップされると、最終的なコードが RTL で生成されます (Verilog および VHDL の両方で)。

コードは、次のヒントの 3 つを使用します。

PIPELINE:II=1オプションで指定された各クロック サイクルでメイン ループ (loop_computeとラベルされている) の実行を要求します。INLINE: 最適化の結果を向上するため、サブ関数を解除します。 これはcompute関数に対して使用されます。INTERFACE: 指定の最上位関数引数のプロトコルを指定します。 これはオプションで、HLS ストリームに AXI4-Stream を追加する方法を示すことのみを目的としています。BIND_STORAGE: 特定のタイプのオンチップ メモリに配列を割り当てます。 ここでは、distance配列は、1 つの書き込みポートと複数の読み出しポートを持つ RAM にマップされ、都市から都市への複数の距離に同時にアクセスして経路全体をよりすばやく計算することを可能にします。

合成を実行する前に、tsp.h ファイルを開いて都市の数を 13 (N=13) に設定します。tsp.h ファイルは、Vitis HLS GUI で tsp.cpp ファイルの #include "tsp.h" 行にマウスを重ね、CTRL キーを押しながらクリックして開くことができます。

GUI から HLS 合成を実行する方法:

C シミュレーションで使用したショートカットを使用して [Run C Synthesis] を選択します。

または、メイン メニューを使用することもできます (Project -> Run C Synthesis -> C Synthesis)。

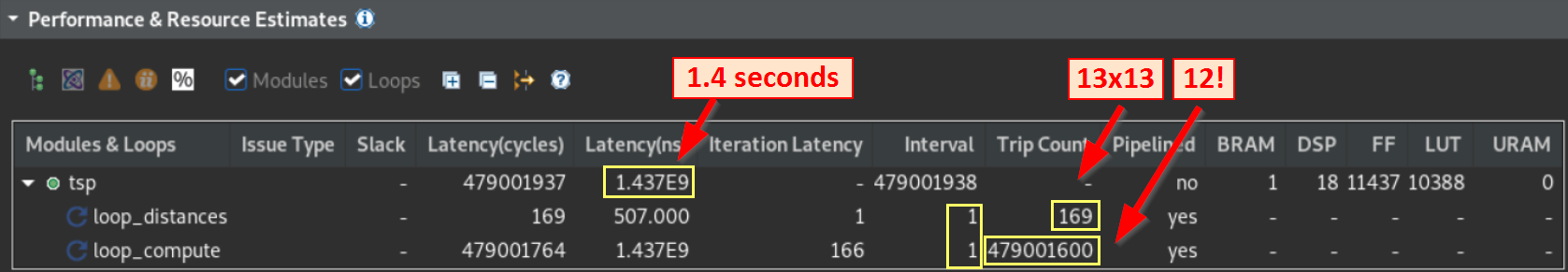

合成が完了すると、メイン ウィンドウに [Performance and Resource Estimates] セクションが表示されます。

([General Information] および [Timing Estimates] セクションは、タイトルをクリックして非展開し、必要に応じてスペースを作成できる)。

この [Performance and Resource Estimates] セクションには表があり、main 関数 tsp およびメイン ループが示されます。これらはソース コードでラベルを付けたため、わかりやすくなっています。

tsp関数の完全なレイテンシは 479,001,957 (約 5 億クロック サイクル) で、これは主にloop_computeからのものです。このレイテンシ 479,001,600 は階乗 12 (12!) で、最初の都市 (経路の始点) が固定されている 13 都市 (N=13) のシナリオに対応するため、置換は残りの 12 都市に適用されます。