Vitis ハードウェア アクセラレーションxilinx.com の Vitis™ 開発環境を参照 |

このセクションの内容

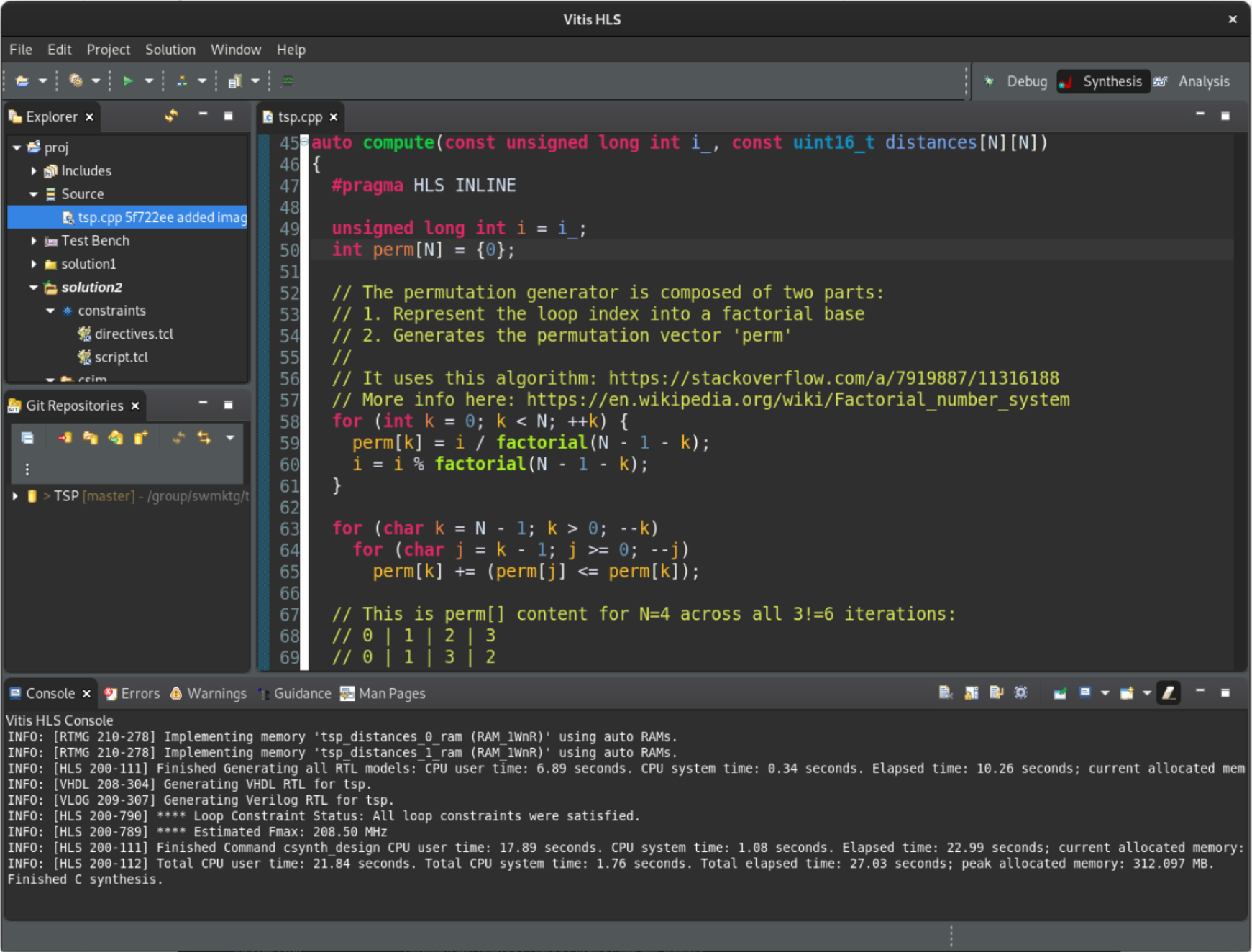

Vitis HLS GUI で C++ の巡回セールスマン問題 (TSP) デザインを読み込みます。

Vitis HLS GUI の起動¶

ターミナルを開いて build ディレクトリに移動し、vitis_hls コマンド (下を参照) を実行します。 Vitis HLS のグラフィカル インターフェイスが開き、hls.tcl (Tcl ファイル) の内容に基づいてプロジェクトがコンフィギュレーションされます。

user@server:~$ cd ./build

user@server:~$ vitis_hls -p hls.tcl &

ツールが表示されたら、左側の [Explorer] ビューで proj->Source を展開します。次に、tsp.cpp をダブルクリックしてソース コードを確認します。

テストベンチは、proj->TestBench のすぐ下の tsp_TB.cpp というファイルにあります。

-p オプションの引数として使用した Tcl ファイル (vitis_hls -p hls.tcl) により、ツールではセットアップおよびコンフィギュレーション オプションの読み出しのみが許可され、シミュレーションまたは合成の実行を必要とするフロー コマンドはスキップされます。

Tcl ファイルの内容は次のとおりです (tsp.cpp およびそのテストベンチ tsp_TB.cpp がプロジェクトにどのように追加されるかを確認)。

# Project setup

#

open_project -reset proj

set_top tsp

add_files ../code/tsp.cpp

add_files -tb ../code/tsp_TB.cpp

# Solution commands

#

open_solution "solution1" -flow_target vivado

set_part {xcvu9p-flga2104-2-i}

create_clock -period 3.0 -name default

set_clock_uncertainty 0.5

config_export -format ip_catalog -rtl verilog

# Main flow commands

#

csim_design

csynth_design

cosim_design

export_design -flow impl -rtl verilog -format syn_dcp

このアクセラレーション関数 tsp は、テストベンチによって関数の外部で計算された一連の整数として距離を受信します。

デザイン構造の説明は、下のリンクをクリックしてください。