ZCU670 Evaluation Kit Tutorial |

Board Setup and Application Deployment |

Setting up the Board and Application Deployment¶

Introduction¶

This document shows how to set up the board and run the ZCU670 Ethernet TRD application with prebuilt images.

Prerequisites¶

Reference design package

zcu670_ethernet_trd_2024.1.zipfileZCU670 Evaluation Board with power cable - 3 nos.

Micro-USB cables for the terminal emulation.

Micro SD cards

UART Driver (FTDI CDM).

Terminal emulator, for example:

Windows: teraterm (Refer to UG1036 regarding Tera Term installation)

Linux: picocom Picocom

25G SFP28 copper cable - 3 nos (SFP28 cable)

Iperf3 (v 3.12) application.

ptp4l (v 4.3)

Board Setup¶

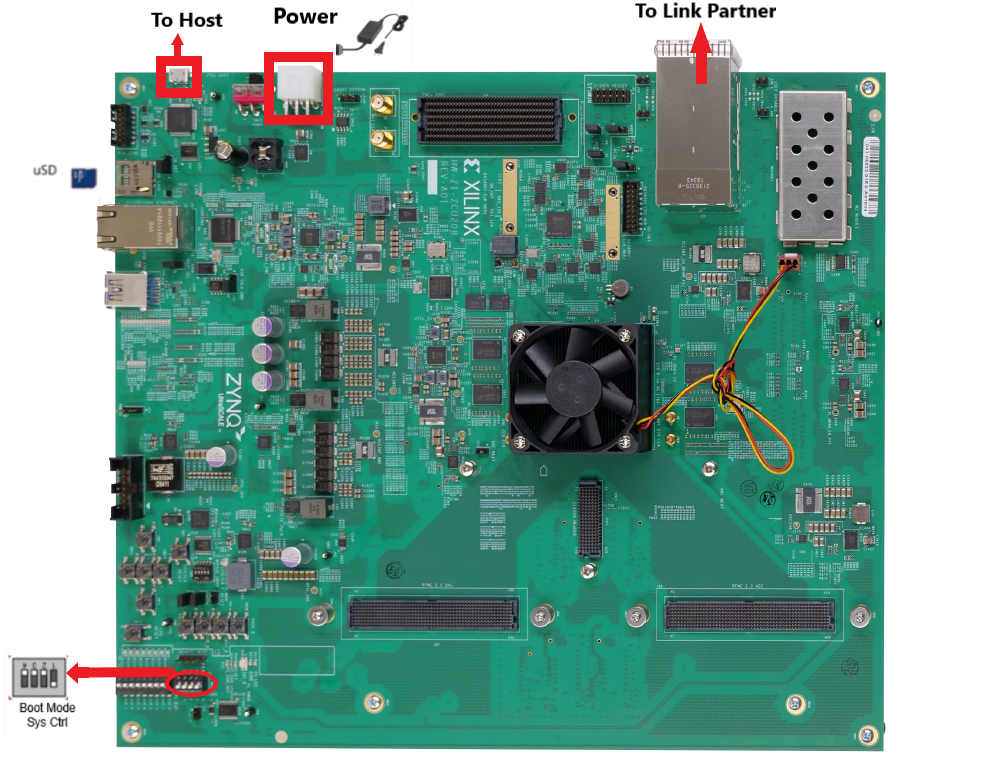

The following figure shows the ZCU670 evaluation board.

Board jumper and switch settings

This is a one-time setup and the board should have been delivered to you with this default setting, however it is good to double check for the first time when you get the board.

Setup Boot Mode switch SW2 to (ON,OFF,OFF,OFF) from switch bits 1 to 4 as shown in the above image to set the board in SD BOOT mode.

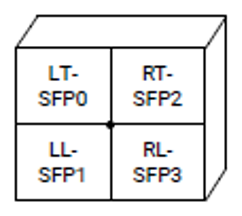

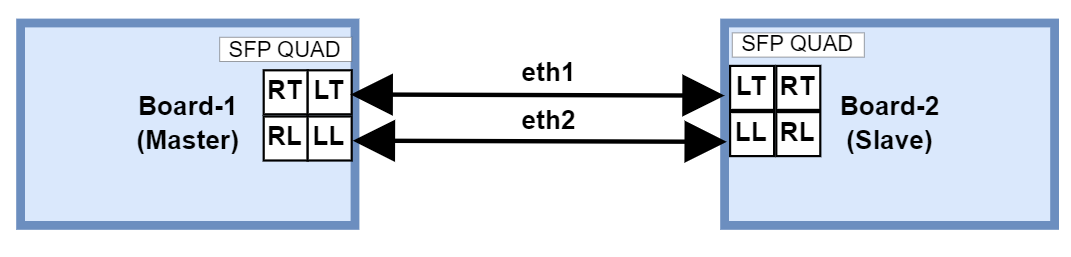

Connect two SFP28 cables between Board-1 and Board-2, connecting the Left Top (LT) slot of one board to other board using a cable and the Left Low (LL) slot of one board to other board using an another cable. The SFP quad (J29) layout diagram is shown below.

Flash the SD Card¶

Unzip the package and save it on your computer.

Navigate to the

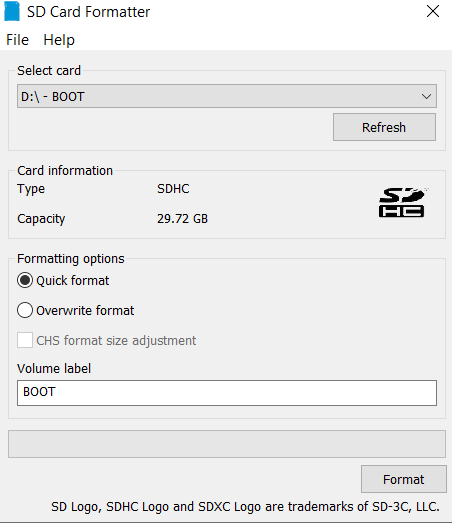

../zcu670-ethernet-trd-2024.1/prebuiltfolder.Prepare the SD card. There are many options to format the SD Card in the windows tool. But, always format with FAT32 option. Use the SD Card Formatter tool to format the SD card SD Card Formatter

.

.Navigate to

zcu670_25G_PTP_subsysorzcu670_10G_PTP_subsysfolder to CopyBOOT.BIN, image.ub and boot.scrto microSD card.Connect the microSD card to the Board.

Repeat steps 3 , 4 and 5 for the second Board.

GT Reference clocks¶

The Renesas 8A34001 synchronization management unit (SMU) chip is the clock source for GT, IEEE 1588 PTP and Synchronous Ethernet (SyncE). For more details on programming and controlling the 8A34001 chip, refer 8A34001 Data sheet.

The GT Reference clock and other clocks required for PTP, syncE are configured by the IDT drivers while booting. The clock configuration files and the binaries used for configuring 8A34001 chip is given in ../zcu670-ethernet-trd-2024.1/IDT folder.

UART Driver Install¶

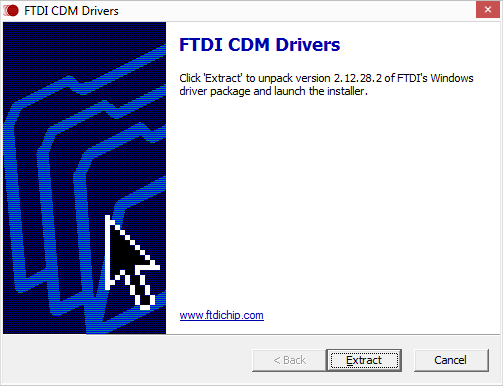

Prior to connecting and powering on the ZCU670, install the FTDI CDM Drivers FTDI CDM Driver

SD Boot Mode:¶

Connect the power supply to the ZCU670 (J52) port and Power on the board

Note: Ensure the Boot Mode switch SW2 to (ON,OFF,OFF,OFF).

Serial console settings

ZCU670 comes with a micro USB connector for JTAG+UART. Connect a Type-A to micro USB cable between the USB UART JTAG (FTDI) connector (J83) of the ZCU670 board and the PC.

The PC will enumerate and shows three COM ports.

UART0 (PS)

UART1 (PL)

System Controller UART

In a terminal emulator, connect to UART0 using the following settings:

Baud Rate: 115200

Data: 8 bit

Parity: None

Stop: 1 bit

Flow Control: None

After a successful boot, a shell prompt will appear as shown below.

xilinx-zcu670-20241 login::

Login with the username petalinux and create a new password when prompted.

To configure the Ethernet interfaces, make sure to log in as super user using the new password created.

xilinx-zcu670-20241:~$:sudo su

Running the applications on board¶

Note: ZCU670 boards include a Renesas 8A34001 SMU chip preloaded with Clock Manager Firmware (CM FW) version 4.8.0. This version does not fully support PTP. To enable proper PTP functionality, update to CM FW 4.9.9 by following AR-000038884

Once the zcu670 boards are booted, set up an IP address for the interface (in this case eth1 and eth2) and make sure the Ethernet link is established between boards. Do not proceed until you are able to ping between boards.

Note: If the link is not established, use the below commands once and ensure the link is up.

ifconfig <interface_name> down

ifconfig <interface_name> <IP-address> up

Note: While making the interface up, make sure a valid IP address is set for the interface.

Synchronous Ethernet (SyncE) commands¶

Note: SyncE test can be performed between ZCU670 and an external protocol tester or other SyncE compatible device.

SyncE master slave Test:¶

In this test two zcu670 boards are used to test the transfer of Synchronization Status Message (SSM) between two boards over the SyncE Ethernet Synchronization Message Channel (ESMC). The test assumes one board as master (Board-1) and the second board (Board-2) as slave.

SyncE Master:

Run synced on master board.

Board-1 > synced -f /usr/bin/synced_master.cfg

Note: To validate the transfer of SSM messages between master and slave boards, Quality level (QL) of master side clock is configured as Primary Reference Time Clock (PRTC) and slave side as Synchronous Equipment Clock (SEC) in order to make the slave device locked to master clock. For more details about syncE configurations refer Renesas SyncE Source.

synced master side log :

The synced log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# synced -f /usr/bin/synced_master.cfg

synced[30032.894]: ---Started synced (version: 2.0.5.310964.b166f770 Mar 21 2024 20:32:02)---

synced[30032.894]: Opened configuration file /usr/bin/synced_master.cfg:

# amd_zcu670.cfg

#

# Global parameters

#

[global]

net_opt 1

no_ql_en 0

synce_forced_ql_en 1

lo_ql PRTC

lo_pri 255

max_msg_lvl 7

stdout_en 1

syslog_en 0

# Device configuration file path (applicable for generic device)

device_cfg_file ""

device_name /dev/rsmu0

synce_dpll_idx 0

holdover_ql PRTC

holdover_tmr 10

hoff_tmr 300

wtr_tmr 10

advanced_holdover_en 0

pcm4l_if_en 1

pcm4l_if_ip_addr 127.0.0.1

pcm4l_if_port_num 2400

mng_if_en 1

mng_if_ip_addr 127.0.0.2

mng_if_port_num 2401

#

# Sync-E clock port

#

[eth1]

clk_idx 1

pri 1

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql PRTC

[eth2]

#clk_idx 255

pri 2

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql PRTC

synced[30032.895]: No QL mode is disabled

synced[30032.895]: eth1 (2E:E6:17:3A:42:2) is Sync-E clock port

synced[30032.895]: eth2 (1E:0D:31:0B:5F:D) is Sync-E monitoring port

synced[30032.895]: Set ESMC network option to 1

synced[30032.895]: Set LO QL to QL-PRTC (1)

synced[30032.895]: Created ESMC configuration

synced[30032.895]: Set Sync-E DPLL index to 0

synced[30032.895]: Created device configuration

synced[30032.895]: Forced QL for Sync-E ports is enabled

synced[30032.895]: Set LO priority to 255

synced[30032.895]: Set hold-off timer to 300 milliseconds

synced[30032.895]: Set wait-to-restore timer to 10 seconds

synced[30032.895]: Set number of syncs to 2

synced[30032.895]: Created control configuration

synced[30032.895]: Set holdover QL to QL-PRTC (1)

synced[30032.895]: Set holdover timer to 10 seconds

synced[30032.895]: Set advanced holdover enable to 0

synced[30032.895]: Created monitor configuration

synced[30032.895]: Initialized management

synced[30032.895]: Initialized device adaptor

synced[30032.895]: Initialized Sync-E DPLL

synced[30032.896]: eth1 is already assigned to clock index 1

synced[30032.896]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[30032.896]: State of clock index 1 associated with port eth1 changed to qualified

synced[30032.896]: Best clock has clock index 1 and rank 0x010100

synced[30032.898]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[30032.898]: Initialized control

synced[30032.898]: Initialized Sync-E DPLL monitor

synced[30032.916]: Opened TX for port eth1 (port number: 5)

synced[30032.966]: Started TX thread for port eth1 (port number: 5)

synced[30032.966]: Created port eth1 (port number: 5) TX

synced[30032.980]: Opened TX for port eth2 (port number: 6)

synced[30033.030]: Started TX thread for port eth2 (port number: 6)

synced[30033.030]: Created port eth2 (port number: 6) TX

synced[30033.030]: Created 2 TX ports

synced[30033.044]: Opened RX for port eth1 (port number: 5)

synced[30033.094]: Started RX thread for port eth1 (port number: 5)

synced[30033.094]: Created port eth1 (port number: 5) RX

synced[30033.108]: Opened RX for port eth2 (port number: 6)

synced[30033.158]: Started RX thread for port eth2 (port number: 6)

synced[30033.158]: Created port eth2 (port number: 6) RX

synced[30033.158]: Created 2 RX ports

synced[30033.158]: Initialized ESMC

synced[30033.208]: pcm4l interface started in 50 milliseconds

synced[30033.258]: Mangement interface started in 50 milliseconds

synced[30033.259]: Current QL set to QL-PRTC (1)

synced[30033.259]: Current Sync-E DPLL state changed to lock acquisition-recovery

synced[30033.259]: pcm4l_if_send: Cannot send message to pcm4l

synced[30033.259]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[30033.259]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30033.259]: Selected port is eth1 and current QL is QL-PRTC (1)

synced[30033.259]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30033.962]: Current Sync-E DPLL state changed to locked

synced[30034.209]: QL changed to QL-DNU (8) on port eth2 (port number: 6)

synced[30034.209]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[30034.209]: Current state for port eth2 changed to normal

synced[30034.209]: Extended QL TLV appeared on port eth2 (port number: 6)

synced[30034.209]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30034.245]: QL changed to QL-DNU (8) on port eth1 (port number: 5)

synced[30034.245]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[30034.245]: Current state for port eth1 changed to normal

synced[30034.245]: Extended QL TLV appeared on port eth1 (port number: 5)

synced[30034.245]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30034.259]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30034.259]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30034.264]: eth2 becomes active Sync-E clock port for clock index 1

synced[30034.264]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[30034.264]: eth1 becomes active Sync-E clock port for clock index 1

synced[30034.264]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[30034.264]: State of clock index 255 associated with port eth2 changed to qualified

synced[30034.264]: Best clock is LO

synced[30034.267]: Set device clock priorities (0): (ordered list of clock indices)

synced[30034.367]: Current Sync-E DPLL state changed to holdover

synced[30034.367]: <<Sent event ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30034.367]: pcm4l_if_send: Cannot send message to pcm4l

synced[30034.367]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[30034.367]: <<Sent event ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30034.367]: Selected port is LO and current QL is QL-PRTC (1)

synced[30034.446]: QL changed to QL-SEC (7) on port eth1 (port number: 5)

synced[30034.446]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[30034.446]: Current state for port eth1 changed to wait-to-restore

synced[30034.446]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30034.460]: QL changed to QL-SEC (7) on port eth2 (port number: 6)

synced[30034.460]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[30034.460]: Current state for port eth2 changed to wait-to-restore

synced[30034.460]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30034.468]: Best clock is LO

synced[30034.470]: Set device clock priorities (0): (ordered list of clock indices)

synced[30035.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30035.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30035.447]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30035.461]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30036.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30036.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30036.412]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30036.449]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30037.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30037.367]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30037.414]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30037.450]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30038.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30038.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30038.415]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30038.451]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30039.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30039.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30039.416]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30039.453]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30040.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30040.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30040.418]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30040.454]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30041.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30041.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30041.419]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30041.456]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30042.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30042.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30042.421]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30042.457]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30043.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30043.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30043.422]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30043.458]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30044.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30044.368]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30044.405]: Current Sync-E DPLL state changed to freerun

synced[30044.423]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30044.460]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30044.505]: Current state for port eth1 changed to normal

synced[30044.505]: Current state for port eth2 changed to normal

synced[30044.505]: Best clock is LO

synced[30044.508]: Set device clock priorities (0): (ordered list of clock indices)

synced[30044.560]: Originator clock timing loop detected on port eth1 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30044.560]: QL changed to QL-DNU (8) on port eth1 (port number: 5)

synced[30044.560]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[30044.560]: Current state for port eth1 changed to normal

synced[30044.560]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30044.574]: Originator clock timing loop detected on port eth2 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30044.574]: QL changed to QL-DNU (8) on port eth2 (port number: 6)

synced[30044.574]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[30044.574]: Current state for port eth2 changed to normal

synced[30044.574]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30044.608]: eth2 becomes active Sync-E clock port for clock index 1

synced[30044.608]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[30044.609]: eth1 becomes active Sync-E clock port for clock index 1

synced[30044.609]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[30044.609]: Best clock is LO

synced[30044.611]: Set device clock priorities (0): (ordered list of clock indices)

synced[30045.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30045.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30045.562]: Originator clock timing loop detected on port eth1 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30045.562]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30045.575]: Originator clock timing loop detected on port eth2 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30045.575]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30046.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30046.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[30046.563]: Originator clock timing loop detected on port eth1 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30046.563]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[30046.577]: Originator clock timing loop detected on port eth2 (ESMC PDU received from MAC address 2E:E6:17:3A:42:2B)

synced[30046.577]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[30047.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[30047.369]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

SyncE Slave:

Run synced on slave board.

Board-2 > synced -f /usr/bin/synced_slave.cfg

synced slave side log :

The synced log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# synced -f /usr/bin/synced_slave.cfg

synced[16703.902]: ---Started synced (version: 2.0.5.310964.b166f770 Mar 21 2024 20:32:02)---

synced[16703.902]: Opened configuration file /usr/bin/synced_slave.cfg:

# amd_zcu670.cfg

#

# Global parameters

#

[global]

net_opt 1

no_ql_en 0

synce_forced_ql_en 1

lo_ql SEC

lo_pri 255

max_msg_lvl 7

stdout_en 1

syslog_en 0

# Device configuration file path (applicable for generic device)

device_cfg_file ""

device_name /dev/rsmu0

synce_dpll_idx 0

holdover_ql SEC

holdover_tmr 10

hoff_tmr 300

wtr_tmr 10

advanced_holdover_en 0

pcm4l_if_en 1

pcm4l_if_ip_addr 127.0.0.1

pcm4l_if_port_num 2400

mng_if_en 1

mng_if_ip_addr 127.0.0.2

mng_if_port_num 2401

#

# Sync-E clock port

#

[eth1]

clk_idx 1

pri 1

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

[eth2]

#clk_idx 255

pri 2

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

synced[16703.903]: No QL mode is disabled

synced[16703.903]: eth1 (F6:B3:9A:9E:C2:4) is Sync-E clock port

synced[16703.903]: eth2 (B6:2C:C2:81:CE:5) is Sync-E monitoring port

synced[16703.903]: Set ESMC network option to 1

synced[16703.903]: Set LO QL to QL-SEC (7)

synced[16703.903]: Created ESMC configuration

synced[16703.903]: Set Sync-E DPLL index to 0

synced[16703.903]: Created device configuration

synced[16703.903]: Forced QL for Sync-E ports is enabled

synced[16703.903]: Set LO priority to 255

synced[16703.903]: Set hold-off timer to 300 milliseconds

synced[16703.903]: Set wait-to-restore timer to 10 seconds

synced[16703.903]: Set number of syncs to 2

synced[16703.903]: Created control configuration

synced[16703.903]: Set holdover QL to QL-SEC (7)

synced[16703.903]: Set holdover timer to 10 seconds

synced[16703.903]: Set advanced holdover enable to 0

synced[16703.903]: Created monitor configuration

synced[16703.903]: Initialized management

synced[16703.903]: Initialized device adaptor

synced[16703.903]: Initialized Sync-E DPLL

synced[16703.904]: eth1 is already assigned to clock index 1

synced[16703.904]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[16703.904]: State of clock index 1 associated with port eth1 changed to qualified

synced[16703.904]: Best clock has clock index 1 and rank 0x070100

synced[16703.906]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[16703.906]: Initialized control

synced[16703.906]: Initialized Sync-E DPLL monitor

synced[16703.924]: Opened TX for port eth1 (port number: 5)

synced[16703.974]: Started TX thread for port eth1 (port number: 5)

synced[16703.974]: Created port eth1 (port number: 5) TX

synced[16703.988]: Opened TX for port eth2 (port number: 6)

synced[16704.038]: Started TX thread for port eth2 (port number: 6)

synced[16704.038]: Created port eth2 (port number: 6) TX

synced[16704.038]: Created 2 TX ports

synced[16704.052]: Opened RX for port eth1 (port number: 5)

synced[16704.102]: Started RX thread for port eth1 (port number: 5)

synced[16704.102]: Created port eth1 (port number: 5) RX

synced[16704.116]: Opened RX for port eth2 (port number: 6)

synced[16704.166]: Started RX thread for port eth2 (port number: 6)

synced[16704.166]: Created port eth2 (port number: 6) RX

synced[16704.166]: Created 2 RX ports

synced[16704.166]: Initialized ESMC

synced[16704.216]: pcm4l interface started in 50 milliseconds

synced[16704.266]: Mangement interface started in 50 milliseconds

synced[16704.267]: Current QL set to QL-SEC (7)

synced[16704.267]: Current Sync-E DPLL state changed to locked

synced[16704.267]: pcm4l_if_send: Cannot send message to pcm4l

synced[16704.267]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[16704.267]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16704.267]: Selected port is eth1 and current QL is QL-SEC (7)

synced[16704.267]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16704.352]: QL changed to QL-DNU (8) on port eth1 (port number: 5)

synced[16704.352]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[16704.352]: Current state for port eth1 changed to normal

synced[16704.352]: Extended QL TLV appeared on port eth1 (port number: 5)

synced[16704.352]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16704.366]: QL changed to QL-DNU (8) on port eth2 (port number: 6)

synced[16704.366]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[16704.366]: Current state for port eth2 changed to normal

synced[16704.366]: Extended QL TLV appeared on port eth2 (port number: 6)

synced[16704.366]: >>Received ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16704.367]: eth2 becomes active Sync-E clock port for clock index 1

synced[16704.368]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[16704.368]: eth1 becomes active Sync-E clock port for clock index 1

synced[16704.368]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[16704.368]: State of clock index 255 associated with port eth2 changed to qualified

synced[16704.368]: Best clock is LO

synced[16704.370]: Set device clock priorities (0): (ordered list of clock indices)

synced[16704.452]: QL changed to QL-PRTC (1) on port eth1 (port number: 5)

synced[16704.452]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[16704.452]: Current state for port eth1 changed to wait-to-restore

synced[16704.452]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16704.466]: QL changed to QL-PRTC (1) on port eth2 (port number: 6)

synced[16704.466]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[16704.466]: Current state for port eth2 changed to wait-to-restore

synced[16704.466]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16704.470]: Current Sync-E DPLL state changed to holdover

synced[16704.471]: pcm4l_if_send: Cannot send message to pcm4l

synced[16704.470]: <<Sent event ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16704.471]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[16704.471]: Selected port is LO and current QL is QL-SEC (7)

synced[16704.471]: <<Sent event ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16704.471]: Best clock is LO

synced[16704.473]: Set device clock priorities (0): (ordered list of clock indices)

synced[16705.454]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16705.468]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16705.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16705.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16706.455]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16706.469]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16706.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16706.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16707.457]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16707.470]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16707.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16707.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16708.458]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16708.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16708.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16708.472]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16709.459]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16709.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16709.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16709.473]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16710.461]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16710.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16710.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16710.475]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16711.462]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16711.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16711.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16711.476]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16712.464]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16712.471]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16712.472]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16712.477]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16713.429]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16713.465]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16713.472]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16713.472]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16714.430]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16714.466]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16714.472]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16714.472]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16714.508]: Current Sync-E DPLL state changed to freerun

synced[16714.509]: Current state for port eth1 changed to normal

synced[16714.509]: Current state for port eth2 changed to normal

synced[16714.509]: Best clock has clock index 1 and rank 0x010101

synced[16714.511]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[16714.612]: Current QL upgraded from QL-SEC (7) to QL-PRTC (1)

synced[16714.612]: Current Sync-E DPLL state changed to lock acquisition-recovery

synced[16714.612]: pcm4l_if_send: Cannot send message to pcm4l

synced[16714.612]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16714.612]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[16714.612]: Selected port is eth1 and current QL is QL-PRTC (1)

synced[16714.612]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16715.431]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16715.468]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16715.516]: Current Sync-E DPLL state changed to locked

synced[16715.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16715.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16716.433]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16716.469]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16716.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16716.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[16717.434]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[16717.471]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[16717.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[16717.612]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

Note:

Current Sync-E DPLL state changed to lockedin the synced log indicate that the slave side DPLL is locked to master and outgoing message quality level is changed to QL-DNU (Do Not Use) to avoild timing loop as configured in thesynced_slave.cfgfile.

SyncE Switching Test¶

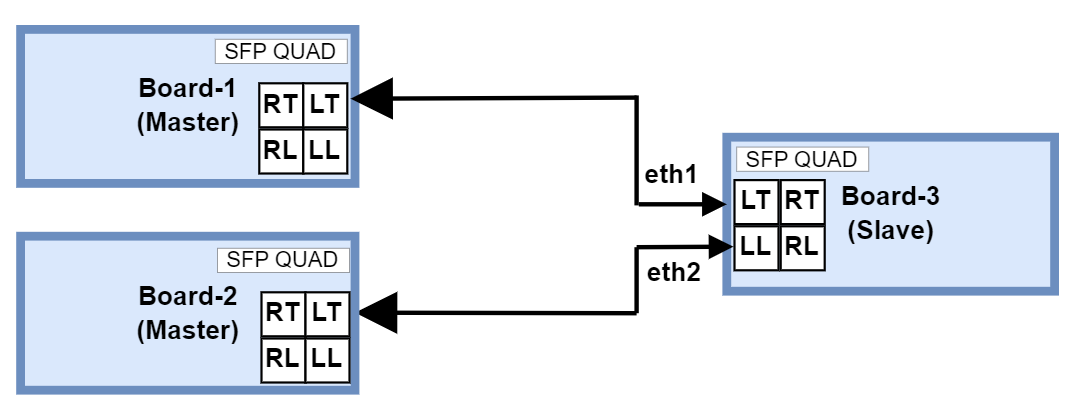

To perform this test three zcu670 boards are used. Two boards (Board-1 & Board-2) are configured as master boards and Board-3 is configured as slave board. The slave board locks to the clock which has better QL by switching the MUX present in gt_shared IP and, select the best recovered clock among the two ethernet interfaces.

Master-1:

Run synced on master board (Board-1).

Board-1 > synced -f /usr/bin/synced_slave.cfg

Note: The QL of Master-1 clock in set to SEC using the

synced_slave.cfgfile

Master-1 side log :

The synced log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# synced -f /usr/bin/synced_slave.cfg

synced[241.458]: ---Started synced (version: 2.0.5.310964.b166f770 Mar 21 2024 20:32:02)---

synced[241.458]: Opened configuration file /usr/bin/synced_slave.cfg:

# amd_zcu670.cfg

#

# Global parameters

#

[global]

net_opt 1

no_ql_en 0

synce_forced_ql_en 1

lo_ql SEC

lo_pri 255

max_msg_lvl 7

stdout_en 1

syslog_en 0

# Device configuration file path (applicable for generic device)

device_cfg_file ""

device_name /dev/rsmu0

synce_dpll_idx 0

holdover_ql SEC

holdover_tmr 10

hoff_tmr 300

wtr_tmr 10

advanced_holdover_en 0

pcm4l_if_en 1

pcm4l_if_ip_addr 127.0.0.1

pcm4l_if_port_num 2400

mng_if_en 1

mng_if_ip_addr 127.0.0.2

mng_if_port_num 2401

#

# Sync-E clock port

#

[eth1]

clk_idx 1

pri 1

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

[eth2]

#clk_idx 255

pri 2

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

synced[241.459]: No QL mode is disabled

synced[241.459]: eth1 (92:14:39:7D:AC:5) is Sync-E clock port

synced[241.459]: eth2 (06:5F:79:AE:58:7) is Sync-E monitoring port

synced[241.459]: Set ESMC network option to 1

synced[241.459]: Set LO QL to QL-SEC (7)

synced[241.459]: Created ESMC configuration

synced[241.459]: Set Sync-E DPLL index to 0

synced[241.459]: Created device configuration

synced[241.459]: Forced QL for Sync-E ports is enabled

synced[241.459]: Set LO priority to 255

synced[241.459]: Set hold-off timer to 300 milliseconds

synced[241.459]: Set wait-to-restore timer to 10 seconds

synced[241.459]: Set number of syncs to 2

synced[241.459]: Created control configuration

synced[241.459]: Set holdover QL to QL-SEC (7)

synced[241.459]: Set holdover timer to 10 seconds

synced[241.459]: Set advanced holdover enable to 0

synced[241.459]: Created monitor configuration

synced[241.459]: Initialized management

synced[241.459]: Initialized device adaptor

synced[241.459]: Initialized Sync-E DPLL

synced[241.460]: eth1 is already assigned to clock index 1

synced[241.460]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[241.460]: State of clock index 1 associated with port eth1 changed to qualified

synced[241.460]: Best clock has clock index 1 and rank 0x070100

synced[241.462]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[241.462]: Initialized control

synced[241.462]: Initialized Sync-E DPLL monitor

synced[241.488]: Opened TX for port eth1 (port number: 5)

synced[241.538]: Started TX thread for port eth1 (port number: 5)

synced[241.538]: Created port eth1 (port number: 5) TX

synced[241.552]: Opened TX for port eth2 (port number: 6)

synced[241.602]: Started TX thread for port eth2 (port number: 6)

synced[241.602]: Created port eth2 (port number: 6) TX

synced[241.602]: Created 2 TX ports

synced[241.616]: Opened RX for port eth1 (port number: 5)

synced[241.666]: Started RX thread for port eth1 (port number: 5)

synced[241.666]: Created port eth1 (port number: 5) RX

synced[241.680]: Opened RX for port eth2 (port number: 6)

synced[241.730]: Started RX thread for port eth2 (port number: 6)

synced[241.730]: Created port eth2 (port number: 6) RX

synced[241.730]: Created 2 RX ports

synced[241.730]: Initialized ESMC

synced[241.780]: pcm4l interface started in 50 milliseconds

synced[241.830]: Mangement interface started in 50 milliseconds

synced[241.831]: Current QL set to QL-SEC (7)

synced[241.831]: Current Sync-E DPLL state changed to lock acquisition-recovery

synced[241.831]: pcm4l_if_send: Cannot send message to pcm4l

synced[241.831]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[241.831]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[241.831]: Selected port is eth1 and current QL is QL-SEC (7)

synced[241.831]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[242.534]: Current Sync-E DPLL state changed to locked

synced[242.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[242.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[243.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[243.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[244.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[244.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[245.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[245.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[246.622]: RX timeout occurred (QL not received within 5 seconds period) on port eth1 (port number: 5)

synced[246.623]: Current state for port eth1 changed to hold-off

synced[246.686]: RX timeout occurred (QL not received within 5 seconds period) on port eth2 (port number: 6)

synced[246.686]: Current state for port eth2 changed to hold-off

synced[246.831]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[246.832]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[246.956]: Current state for port eth1 changed to normal

synced[246.957]: eth2 becomes active Sync-E clock port for clock index 1

synced[246.957]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[246.957]: State of clock index 1 associated with port eth2 changed to qualified

synced[246.957]: Best clock has clock index 1 and rank 0x070200

synced[246.959]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[247.060]: pcm4l_if_send: Cannot send message to pcm4l

synced[247.060]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[247.060]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[247.060]: Selected port is eth2 and current QL is QL-SEC (7)

synced[247.060]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[247.060]: Current state for port eth2 changed to normal

synced[247.060]: eth1 becomes active Sync-E clock port for clock index 1

synced[247.060]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[247.060]: Best clock is LO

synced[247.062]: Set device clock priorities (0): (ordered list of clock indices)

synced[247.163]: Current Sync-E DPLL state changed to holdover

synced[247.163]: pcm4l_if_send: Cannot send message to pcm4l

synced[247.163]: <<Sent event ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[247.163]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[247.163]: Selected port is LO and current QL is QL-SEC (7)

synced[247.163]: <<Sent event ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[248.163]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[248.163]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[249.163]: <<Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)>>

Note:

Sent information ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)in master-1 side log indicate syncE message with quality level SEC on eth1 interface.

Master-2:

Run synced on master board.

Board-2 > synced -f /usr/bin/synced_master.cfg

Note: The QL of master-2 clock in set to PRTC using the synced_master.cfg file

Master-2 side log :

The synced log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# synced -f /usr/bin/synced_master.cfg

synced[232.226]: ---Started synced (version: 2.0.5.310964.b166f770 Mar 21 2024 20:32:02)---

synced[232.226]: Opened configuration file /usr/bin/synced_master.cfg:

# amd_zcu670.cfg

#

# Global parameters

#

[global]

net_opt 1

no_ql_en 0

synce_forced_ql_en 1

lo_ql PRTC

lo_pri 255

max_msg_lvl 7

stdout_en 1

syslog_en 0

# Device configuration file path (applicable for generic device)

device_cfg_file ""

device_name /dev/rsmu0

synce_dpll_idx 0

holdover_ql PRTC

holdover_tmr 10

hoff_tmr 300

wtr_tmr 10

advanced_holdover_en 0

pcm4l_if_en 1

pcm4l_if_ip_addr 127.0.0.1

pcm4l_if_port_num 2400

mng_if_en 1

mng_if_ip_addr 127.0.0.2

mng_if_port_num 2401

#

# Sync-E clock port

#

[eth1]

clk_idx 1

pri 1

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql PRTC

[eth2]

#clk_idx 255

pri 2

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql PRTC

synced[232.227]: No QL mode is disabled

synced[232.227]: eth1 (FE:15:3E:41:F3:9) is Sync-E clock port

synced[232.227]: eth2 (12:4D:DF:F7:3C:1) is Sync-E monitoring port

synced[232.227]: Set ESMC network option to 1

synced[232.227]: Set LO QL to QL-PRTC (1)

synced[232.227]: Created ESMC configuration

synced[232.227]: Set Sync-E DPLL index to 0

synced[232.227]: Created device configuration

synced[232.227]: Forced QL for Sync-E ports is enabled

synced[232.227]: Set LO priority to 255

synced[232.227]: Set hold-off timer to 300 milliseconds

synced[232.227]: Set wait-to-restore timer to 10 seconds

synced[232.227]: Set number of syncs to 2

synced[232.227]: Created control configuration

synced[232.227]: Set holdover QL to QL-PRTC (1)

synced[232.227]: Set holdover timer to 10 seconds

synced[232.227]: Set advanced holdover enable to 0

synced[232.227]: Created monitor configuration

synced[232.227]: Initialized management

synced[232.227]: Initialized device adaptor

synced[232.227]: Initialized Sync-E DPLL

synced[232.228]: eth1 is already assigned to clock index 1

synced[232.228]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[232.228]: State of clock index 1 associated with port eth1 changed to qualified

synced[232.228]: Best clock has clock index 1 and rank 0x010100

synced[232.230]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[232.230]: Initialized control

synced[232.230]: Initialized Sync-E DPLL monitor

synced[232.252]: Opened TX for port eth1 (port number: 5)

synced[232.302]: Started TX thread for port eth1 (port number: 5)

synced[232.302]: Created port eth1 (port number: 5) TX

synced[232.316]: Opened TX for port eth2 (port number: 6)

synced[232.366]: Started TX thread for port eth2 (port number: 6)

synced[232.366]: Created port eth2 (port number: 6) TX

synced[232.366]: Created 2 TX ports

synced[232.380]: Opened RX for port eth1 (port number: 5)

synced[232.430]: Started RX thread for port eth1 (port number: 5)

synced[232.430]: Created port eth1 (port number: 5) RX

synced[232.452]: Opened RX for port eth2 (port number: 6)

synced[232.502]: Started RX thread for port eth2 (port number: 6)

synced[232.502]: Created port eth2 (port number: 6) RX

synced[232.502]: Created 2 RX ports

synced[232.502]: Initialized ESMC

synced[232.552]: pcm4l interface started in 50 milliseconds

synced[232.602]: Mangement interface started in 50 milliseconds

synced[232.603]: Current QL set to QL-PRTC (1)

synced[232.603]: Current Sync-E DPLL state changed to lock acquisition-recovery

synced[232.603]: pcm4l_if_send: Cannot send message to pcm4l

synced[232.603]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[232.603]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[232.603]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[232.603]: Selected port is eth1 and current QL is QL-PRTC (1)

synced[233.306]: Current Sync-E DPLL state changed to locked

synced[233.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[233.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[234.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[234.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[235.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[235.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[236.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[236.603]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[237.386]: RX timeout occurred (QL not received within 5 seconds period) on port eth1 (port number: 5)

synced[237.386]: Current state for port eth1 changed to hold-off

synced[237.458]: RX timeout occurred (QL not received within 5 seconds period) on port eth2 (port number: 6)

synced[237.458]: Current state for port eth2 changed to hold-off

synced[237.604]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[237.604]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[237.728]: Current state for port eth1 changed to normal

synced[237.728]: eth2 becomes active Sync-E clock port for clock index 1

synced[237.728]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[237.729]: State of clock index 1 associated with port eth2 changed to qualified

synced[237.729]: Best clock has clock index 1 and rank 0x010200

synced[237.731]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[237.831]: pcm4l_if_send: Cannot send message to pcm4l

synced[237.831]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[237.832]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[237.832]: Selected port is eth2 and current QL is QL-PRTC (1)

synced[237.832]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[237.832]: Current state for port eth2 changed to normal

synced[237.832]: eth1 becomes active Sync-E clock port for clock index 1

synced[237.832]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[237.832]: Best clock is LO

synced[237.834]: Set device clock priorities (0): (ordered list of clock indices)

synced[237.934]: Current Sync-E DPLL state changed to holdover

synced[237.935]: pcm4l_if_send: Cannot send message to pcm4l

synced[237.934]: <<Sent event ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[237.935]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[237.935]: Selected port is LO and current QL is QL-PRTC (1)

synced[237.935]: <<Sent event ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[238.935]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[238.935]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[239.935]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[239.935]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[240.935]: <<Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)>>

Note:

Sent information ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth1 (port number: 5)in master-2 side log indicate syncE message with quality level PRTC on eth1 interface.

Slave:

Run synced on slave board.

Board-3 > synced -f /usr/bin/synced_slave.cfg

synced slave side log :

The synced log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# synced -f /usr/bin/synced_slave.cfg

synced[246.410]: ---Started synced (version: 2.0.5.310964.b166f770 Mar 21 2024 20:32:02)---

synced[246.410]: Opened configuration file /usr/bin/synced_slave.cfg:

# amd_zcu670.cfg

#

# Global parameters

#

[global]

net_opt 1

no_ql_en 0

synce_forced_ql_en 1

lo_ql SEC

lo_pri 255

max_msg_lvl 7

stdout_en 1

syslog_en 0

# Device configuration file path (applicable for generic device)

device_cfg_file ""

device_name /dev/rsmu0

synce_dpll_idx 0

holdover_ql SEC

holdover_tmr 10

hoff_tmr 300

wtr_tmr 10

advanced_holdover_en 0

pcm4l_if_en 1

pcm4l_if_ip_addr 127.0.0.1

pcm4l_if_port_num 2400

mng_if_en 1

mng_if_ip_addr 127.0.0.2

mng_if_port_num 2401

#

# Sync-E clock port

#

[eth1]

clk_idx 1

pri 1

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

[eth2]

#clk_idx 255

pri 2

tx_en 1

rx_en 1

tx_bundle_num 0

init_ql SEC

synced[246.411]: No QL mode is disabled

synced[246.411]: eth1 (62:A2:12:A0:76:B) is Sync-E clock port

synced[246.411]: eth2 (F2:4F:21:0A:5A:9) is Sync-E monitoring port

synced[246.411]: Set ESMC network option to 1

synced[246.411]: Set LO QL to QL-SEC (7)

synced[246.411]: Created ESMC configuration

synced[246.411]: Set Sync-E DPLL index to 0

synced[246.411]: Created device configuration

synced[246.411]: Forced QL for Sync-E ports is enabled

synced[246.411]: Set LO priority to 255

synced[246.411]: Set hold-off timer to 300 milliseconds

synced[246.411]: Set wait-to-restore timer to 10 seconds

synced[246.411]: Set number of syncs to 2

synced[246.411]: Created control configuration

synced[246.411]: Set holdover QL to QL-SEC (7)

synced[246.411]: Set holdover timer to 10 seconds

synced[246.411]: Set advanced holdover enable to 0

synced[246.411]: Created monitor configuration

synced[246.411]: Initialized management

synced[246.411]: Initialized device adaptor

synced[246.411]: Initialized Sync-E DPLL

synced[246.412]: eth1 is already assigned to clock index 1

synced[246.412]: management_example_ext_mux_control: selected port eth1 on external mux 0 for primary clock index 1

synced[246.412]: State of clock index 1 associated with port eth1 changed to qualified

synced[246.412]: Best clock has clock index 1 and rank 0x070100

synced[246.414]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[246.414]: Initialized control

synced[246.414]: Initialized Sync-E DPLL monitor

synced[246.440]: Opened TX for port eth1 (port number: 5)

synced[246.490]: Started TX thread for port eth1 (port number: 5)

synced[246.490]: Created port eth1 (port number: 5) TX

synced[246.504]: Opened TX for port eth2 (port number: 6)

synced[246.554]: Started TX thread for port eth2 (port number: 6)

synced[246.554]: Created port eth2 (port number: 6) TX

synced[246.554]: Created 2 TX ports

synced[246.576]: Opened RX for port eth1 (port number: 5)

synced[246.626]: Started RX thread for port eth1 (port number: 5)

synced[246.626]: Created port eth1 (port number: 5) RX

synced[246.640]: Opened RX for port eth2 (port number: 6)

synced[246.690]: Started RX thread for port eth2 (port number: 6)

synced[246.690]: Created port eth2 (port number: 6) RX

synced[246.690]: Created 2 RX ports

synced[246.690]: Initialized ESMC

synced[246.740]: pcm4l interface started in 50 milliseconds

synced[246.790]: Mangement interface started in 50 milliseconds

synced[246.791]: Current QL set to QL-SEC (7)

synced[246.791]: Current Sync-E DPLL state changed to lock acquisition-recovery

synced[246.791]: pcm4l_if_send: Cannot send message to pcm4l

synced[246.791]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[246.791]: pcm4l_msg_set_clock_category: clock category 4 - not sent to pcm4l

synced[246.791]: Selected port is eth1 and current QL is QL-SEC (7)

synced[246.791]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[247.140]: QL changed to QL-PRTC (1) on port eth2 (port number: 6)

synced[247.140]: Extended QL TLV data changed on port eth2 (port number: 6)

synced[247.140]: Current state for port eth2 changed to normal

synced[247.140]: Extended QL TLV appeared on port eth2 (port number: 6)

synced[247.140]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[247.193]: eth2 becomes active Sync-E clock port for clock index 1

synced[247.193]: management_example_ext_mux_control: selected port eth2 on external mux 0 for primary clock index 1

synced[247.193]: Best clock has clock index 1 and rank 0x010201

synced[247.195]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[247.296]: Current QL upgraded from QL-SEC (7) to QL-PRTC (1)

synced[247.296]: pcm4l_if_send: Cannot send message to pcm4l

synced[247.296]: pcm4l_msg_set_clock_category: clock category 1 - not sent to pcm4l

synced[247.296]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[247.296]: Selected port is eth2 and current QL is QL-PRTC (1)

synced[247.296]: <<Sent event ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[247.296]: State of clock index 1 associated with port eth2 changed to qualified

synced[247.327]: QL changed to QL-SEC (7) on port eth1 (port number: 5)

synced[247.327]: Extended QL TLV data changed on port eth1 (port number: 5)

synced[247.327]: Extended QL TLV appeared on port eth1 (port number: 5)

synced[247.327]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[247.397]: Best clock has clock index 1 and rank 0x010201

synced[247.399]: Set device clock priorities (1): 1 (ordered list of clock indices)

synced[247.500]: Current Sync-E DPLL state changed to locked

synced[248.142]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[248.296]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[248.296]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[248.328]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[249.143]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[249.296]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

synced[249.296]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth2 (port number: 6)>>

synced[249.330]: >>Received ESMC PDU with QL-SEC (7) (extended QL TLV: yes) on port eth1 (port number: 5)<<

synced[250.145]: >>Received ESMC PDU with QL-PRTC (1) (extended QL TLV: yes) on port eth2 (port number: 6)<<

synced[250.296]: <<Sent information ESMC PDU with QL-DNU (8) (extended QL TLV: yes) on port eth1 (port number: 5)>>

Note:

Current QL upgraded from QL-SEC (7) to QL-PRTC (1)in slave side log indicates syncE has switched the external MUX and, the clock port ofeth2is selected as primary clock.

PPS commands¶

To enable PPS signal from Renesas ClockMatrix PHC :

> testptp -d /dev/ptp0 -i 2 -p 1000000000

To check the PPS external timestamp event of AMD Timer-Syncer PHC:

> testptp -e 10 -d /dev/ptp1

Note: Make sure to re-enable PPS after running ts2phc, as it temporarily disables PPS during execution.

testptp log :

xilinx-zcu670-20241:/home/petalinux# testptp -e 10 -d /dev/ptp1

external time stamp request okay

event index 0 at 3264.000000434

event index 0 at 3265.000000434

event index 0 at 3266.000000434

event index 0 at 3267.000000434

event index 0 at 3268.000000434

event index 0 at 3269.000000434

event index 0 at 3270.000000434

event index 0 at 3271.000000434

event index 0 at 3272.000000434

event index 0 at 3273.000000434

PTP commands¶

Note: PTP commands in this section are given assuming one board as master (Board-1) and the second board as slave (Board-2).

Phase Synchronization¶

PTP phase synchronization commands given in this section uses the ITU-T profile G.8275.1 and ITU-T G.8275.2 config files. The ITU-T profile for PTP is designed to meet the frequency and time synchronization requirements of telecom networks.

Note: PTP test commands are given assuming the zcu670 board as Time Slave clock (T-SC), the same test can be performed considering the board as boundary clock (T-BC) using suitable ITU-T config files.

Multicast Mode (G.8275.1):¶

G.8275.1 profile transport PTP packets directly over L2 ethernet for accurate synchronization of time and phase. This profile is used for networks with full timing support, where every network element participates in PTP.

Master:

Run ts2phc between Renesas ClockMatrix PHC and AMD Timer-Syncer PHC in background:

Board-1 > ts2phc -mqf /usr/bin/zcu670_ts2phc.cfg &

Run ptp4l using G.8275.1 configuration on master board:

Board-1 > ptp4l -i <interface-name> -f /usr/bin/linkpartner_G.8275.1.cfg -m

ptp4l master side log :

xilinx-zcu670-20241:/home/petalinux# ptp4l -i eth1 -f /usr/bin/linkpartner_G.8275.1.cfg -m

option masterOnly is deprecated, please use serverOnly instead

ptp4l[13018.067]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[13018.068]: selected /dev/ptp1 as PTP clock

ptp4l[13018.120]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[13018.120]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[13018.120]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[13018.533]: port 1 (eth1): LISTENING to MASTER on ANNOUNCE_RECEIPT_TIMEOUT_EXPIRES

ptp4l[13018.534]: selected local clock 8215f9.fffe.ca805f as best master

ptp4l[13018.534]: port 1 (eth1): assuming the grand master role

Slave:

Run ts2phc between Renesas ClockMatrix PHC and AMD Timer-Syncer PHC in background:

Board-2 > ts2phc -mqf /usr/bin/zcu670_ts2phc.cfg &

Run ptp4l using G.8275.1 configuration on slave board:

Note: Ensure that only one instance of ptp4l master is running in Link partner.

Board-2 > ptp4l -mqf /usr/bin/standalone_G.8275.1.cfg -p /dev/ptp0

Note: Interface name in

standalone_G.8275.1.cfgis configured aseth1, change the interface name while running it on other interface.

ptp4l phase synchronization log :

xilinx-zcu670-20241:/home/petalinux# ptp4l -mqf /usr/bin/standalone_G.8275.1.cfg -p /dev/ptp0

option masterOnly is deprecated, please use serverOnly instead

option slaveOnly is deprecated, please use clientOnly instead

ptp4l[12781.908]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[12781.908]: selected /dev/ptp0 as PTP clock

ptp4l[12781.910]: port 1 (eth1): taking /dev/ptp0 from the command line, not the attached ptp1

ptp4l[12781.952]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[12781.952]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[12781.952]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[12781.952]: port 1 (eth1): taking /dev/ptp0 from the command line, not the attached ptp1

ptp4l[12782.076]: port 1 (eth1): new foreign master 8215f9.fffe.ca805f-1

ptp4l[12782.326]: selected best master clock 8215f9.fffe.ca805f

ptp4l[12782.326]: port 1 (eth1): LISTENING to UNCALIBRATED on RS_SLAVE

ptp4l[12788.704]: port 1 (eth1): UNCALIBRATED to SLAVE on MASTER_CLOCK_SELECTED

ptp4l[12789.391]: rms 177395279808 max 354790559620 freq -115 +/- 81 delay 171 +/- 2

ptp4l[12790.392]: rms 25 max 34 freq -13 +/- 32 delay 173 +/- 1

ptp4l[12791.392]: rms 23 max 33 freq +31 +/- 2 delay 174 +/- 1

ptp4l[12792.393]: rms 6 max 13 freq +21 +/- 6 delay 174 +/- 1

ptp4l[12793.393]: rms 2 max 3 freq +12 +/- 2 delay 174 +/- 1

ptp4l[12794.393]: rms 3 max 5 freq +10 +/- 4 delay 174 +/- 1

ptp4l[12795.394]: rms 1 max 2 freq +10 +/- 2 delay 174 +/- 1

ptp4l[12796.394]: rms 2 max 5 freq +11 +/- 4 delay 174 +/- 1

Unicast Mode (G.8275.2):¶

G.8275. 2 profile transport PTP packets over IPv4 or IPv6 in unicast mode. It is aimed at operating in existing network not necessarily all devices in the network are PTP aware.

Master:

Run ts2phc between Renesas ClockMatrix PHC and AMD Timer-Syncer PHC in background:

Board-1 > ts2phc -mqf /usr/bin/zcu670_ts2phc.cfg &

Run ptp4l using G.8275.2 configuration on master board:

Board-1 > ptp4l -i <interface-name> -m -f /usr/local/etc/ptp4l/zcu670_unicast_master.cfg &

ptp4l master side log :

xilinx-zcu670-20241:/home/petalinux# ptp4l -i eth1 -m -f /usr/local/etc/ptp4l/zcu670_unicast_master.cfg

option slaveOnly is deprecated, please use clientOnly instead

option masterOnly is deprecated, please use serverOnly instead

ptp4l[5457.096]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[5457.096]: selected /dev/ptp1 as PTP clock

ptp4l[5457.097]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5457.097]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5457.097]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5461.497]: port 1 (eth1): LISTENING to MASTER on ANNOUNCE_RECEIPT_TIMEOUT_EXPIRES

ptp4l[5461.497]: selected local clock 0ec438.fffe.4dda81 as best master

ptp4l[5461.497]: port 1 (eth1): assuming the grand master role

Slave:

Run ts2phc between Renesas ClockMatrix PHC and AMD Timer-Syncer PHC in background:

Board-2 > ts2phc -mqf /usr/bin/zcu670_ts2phc.cfg &

Run ptp4l using G.8275.2 configuration on slave board:

Note: Before running ptp4l on the slave board, add the master’s UDPv4 IP to unicast_master_table in the

zcu670_standalone_unicast_1port.cfgconfig file. Also, update the default interface eth1 if using a different one.

Board-2 > ptp4l -mqf /usr/local/etc/ptp4l/zcu670_standalone_unicast_1port.cfg -p /dev/ptp0

Note: Ensure that only one instance of ptp4l master is running in Link partner.

ptp4l phase synchronization log :

xilinx-zcu670-20241:/home/petalinux# ptp4l -mqf /usr/local/etc/ptp4l/zcu670_standalone_unicast_1port.cfg -p /dev/ptp0

option slaveOnly is deprecated, please use clientOnly instead

option masterOnly is deprecated, please use serverOnly instead

ptp4l[5514.664]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[5514.664]: selected /dev/ptp0 as PTP clock

ptp4l[5514.666]: port 1 (eth1): taking /dev/ptp0 from the command line, not the attached ptp1

ptp4l[5514.667]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5514.667]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5514.667]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[5514.667]: port 1 (eth1): taking /dev/ptp0 from the command line, not the attached ptp1

ptp4l[5516.013]: port 1 (eth1): new foreign master 0ec438.fffe.4dda81-1

ptp4l[5519.924]: selected local clock b69a81.fffe.30b74a as best master

ptp4l[5520.013]: selected best master clock 0ec438.fffe.4dda81

ptp4l[5520.013]: port 1 (eth1): LISTENING to UNCALIBRATED on RS_SLAVE

ptp4l[5526.355]: port 1 (eth1): UNCALIBRATED to SLAVE on MASTER_CLOCK_SELECTED

ptp4l[5527.042]: rms 5720717720 max 11441435445 freq -154 +/- 106 delay 169 +/- 3

ptp4l[5528.043]: rms 25 max 37 freq -47 +/- 40 delay 169 +/- 2

ptp4l[5529.043]: rms 32 max 37 freq +26 +/- 8 delay 172 +/- 0

ptp4l[5530.043]: rms 18 max 22 freq +41 +/- 5 delay 173 +/- 0

ptp4l[5531.044]: rms 4 max 7 freq +30 +/- 5 delay 173 +/- 0

ptp4l[5532.044]: rms 5 max 6 freq +15 +/- 3 delay 171 +/- 0

ptp4l[5533.044]: rms 4 max 6 freq +12 +/- 3 delay 172 +/- 0

ptp4l[5534.045]: rms 2 max 4 freq +16 +/- 3 delay 172 +/- 1

ptp4l[5535.045]: rms 3 max 5 freq +24 +/- 2 delay 172 +/- 0

ptp4l[5536.046]: rms 2 max 3 freq +18 +/- 2 delay 172 +/- 1

ptp4l[5537.046]: rms 2 max 4 freq +20 +/- 3 delay 172 +/- 0

ptp4l[5538.046]: rms 2 max 4 freq +22 +/- 4 delay 172 +/- 0

ptp4l[5539.047]: rms 3 max 7 freq +29 +/- 3 delay 172 +/- 0

PTP clock manager for Linux (pcm4l)¶

Renesas pcm4l utility, has external servo and Packet Delay Variation (PDV) filters specifically meant for the functional requirements of ITU-telecom profile specifications.

Note: For

pcm4ltests, thets2phcutility used to sync Renesas ClockMatrix PHC and AMD Timer-Syncer PHC is replaced bypcm4l. Ensure allts2phcinstances are terminated before runningpcm4l.

Multicast Mode(G.8275.1):¶

Master:

Run ts2phc between Renesas ClockMatrix PHC and AMD Timer-Syncer PHC in background:

Board-1 > ts2phc -mqf /usr/bin/zcu670_ts2phc.cfg &

Run ptp4l using G.8275.1 configuration on master board:

Board -1 > ptp4l -i <interface-name> -m -f /usr/local/etc/ptp4l/zcu670_multicast_master.cfg

ptp4l master side log:

xilinx-zcu670-20241:/home/petalinux# ptp4l -i eth1 -m -f /usr/local/etc/ptp4l/zcu670_multicast_master.cfg

option slaveOnly is deprecated, please use clientOnly instead

option masterOnly is deprecated, please use serverOnly instead

ptp4l[260.319]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[260.320]: selected /dev/ptp1 as PTP clock

ptp4l[260.364]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[260.364]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[260.364]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[260.815]: port 1 (eth1): LISTENING to MASTER on ANNOUNCE_RECEIPT_TIMEOUT_EXPIRES

ptp4l[260.816]: selected local clock 4ad1c5.fffe.4721fe as best master

ptp4l[260.816]: port 1 (eth1): assuming the grand master role

Slave:

Run ptp4l enabling external servo on slave board:

Board -2 > ptp4l -mqf /usr/local/etc/ptp4l/zcu670_externServo_multicast_1port.cfg -p /dev/ptp0 &

Note: Interface name in

zcu670_externServo_multicast_1port.cfgis configured aseth1, change the interface name while running it on other interface.

ptp4l slave side log:

xilinx-zcu670-20241:/home/petalinux# ptp4l -mqf /usr/local/etc/ptp4l/zcu670_externServo_multicast_1port.cfg -p /dev/ptp0 &

[1] 659

option slaveOnly is deprecated, please use clientOnly instead

xilinx-zcu670-20241:/home/petalinux# option masterOnly is deprecated, please use serverOnly instead

ptp4l[1526.464]: ioctl SIOCETHTOOL failed: Operation not supported

ptp4l[1526.504]: port 1 (eth1): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[1526.504]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[1526.504]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETE

ptp4l[1526.539]: port 1 (eth1): new foreign master 4ad1c5.fffe.4721fe-1

ptp4l[1526.789]: selected best master clock 4ad1c5.fffe.4721fe

ptp4l[1526.789]: port 1 (eth1): LISTENING to UNCALIBRATED on RS_SLAVE

ptp4l[1528.852]: master offset 1758718775620075969 s0 freq +24 path delay 170

ptp4l[1530.853]: master offset 1758718775620076027 s0 freq +29 path delay 173

ptp4l[1532.854]: master offset 1758718775620076055 s0 freq +14 path delay 171

ptp4l[1534.854]: master offset 1758718775620076124 s0 freq +33 path delay 171

ptp4l[1536.855]: master offset 1758718775620076176 s0 freq +26 path delay 171

ptp4l[1538.856]: master offset 1758718775620076230 s0 freq +27 path delay 169

ptp4l[1540.857]: master offset 1758718775620076267 s0 freq +19 path delay 173

ptp4l[1542.857]: master offset 1758718775620076294 s0 freq +13 path delay 171

ptp4l[1544.858]: master offset 1758718775620076342 s0 freq +24 path delay 171

ptp4l[1546.859]: master offset 1758718775620076384 s0 freq +21 path delay 171

ptp4l[1548.860]: master offset 1758718775620076430 s0 freq +24 path delay 171

Note: PTP clock servo state remains in unlocked state (s0), expecting pcm4l to control the servo.

Run pcm4l:

Board -2 > pcm4l -f /usr/local/etc/pcm4l/zcu670_reConfigPCM_G8273_2.json

Note: If you see RE::SyncError messages related to PPS while running pcm4l, enable PPS using

testptp -d /dev/ptp0 -i 2 -p 1000000000

pcm4l log:

The pcm4l log is given below.

Click to expand

xilinx-zcu670-20241:/home/petalinux# pcm4l -f /usr/local/etc/pcm4l/zcu670_reConfigPCM_G8273_2.json

The file is /usr/local/etc/pcm4l/zcu670_reConfigPCM_G8273_2.json

JSON file: /usr/local/etc/pcm4l/zcu670_reConfigPCM_G8273_2.json

Initialize default configuration values for linux Extern

Start Logger

RE::SyncAnalysis: 2025-09-24 13:04:36 880301365 ns [0, Main] (3561) RE PTP Software Release ID = 4.3.4.518632, Commit ID = 07229d8c4548eebfbdb068ff4fef304398b817ba Jul 31 2025 12:40:52

RE::SyncAnalysis: 2025-09-24 13:04:36 880378016 ns [0, Main] (3561) Configuration file: /usr/local/etc/pcm4l/zcu670_reConfigPCM_G8273_2.json

RE::SyncAnalysis: 2025-09-24 13:04:36 880402616 ns [0, Main] (3561) {

RE::SyncAnalysis: 2025-09-24 13:04:36 880423636 ns [0, Main] (3561) "versionId": "4.3",

RE::SyncAnalysis: 2025-09-24 13:04:36 880448506 ns [0, Main] (3561) "testModeEnable": 0,

RE::SyncAnalysis: 2025-09-24 13:04:36 880472407 ns [0, Main] (3561) "referenceTrackerType": "WritePhase",

RE::SyncAnalysis: 2025-09-24 13:04:36 880497967 ns [0, Main] (3561) "remoteUdsAddress": "/var/run/ptp4l",

RE::SyncAnalysis: 2025-09-24 13:04:36 880520487 ns [0, Main] (3561) "localUdsAddress": "/var/run/pcm4l",

RE::SyncAnalysis: 2025-09-24 13:04:36 880541877 ns [0, Main] (3561) "mngApiTimeoutMilliseconds": 100,

RE::SyncAnalysis: 2025-09-24 13:04:36 880563937 ns [0, Main] (3561) "stepWindowSeconds": 1,

RE::SyncAnalysis: 2025-09-24 13:04:36 880588208 ns [0, Main] (3561) "phc4lConfig":

RE::SyncAnalysis: 2025-09-24 13:04:36 880610668 ns [0, Main] (3561) {

RE::SyncAnalysis: 2025-09-24 13:04:36 880632038 ns [0, Main] (3561) "dcoDevice": "/dev/ptp0",

RE::SyncAnalysis: 2025-09-24 13:04:36 880652458 ns [0, Main] (3561) "tsDevice":

RE::SyncAnalysis: 2025-09-24 13:04:36 880672279 ns [0, Main] (3561) [

RE::SyncAnalysis: 2025-09-24 13:04:36 880692139 ns [0, Main] (3561) {

RE::SyncAnalysis: 2025-09-24 13:04:36 880711629 ns [0, Main] (3561) "tsDeviceName": "/dev/ptp1",

RE::SyncAnalysis: 2025-09-24 13:04:36 880733349 ns [0, Main] (3561) "tsDevicePinIndex": -1,

RE::SyncAnalysis: 2025-09-24 13:04:36 880754009 ns [0, Main] (3561) "tsDeviceExttsChannel": 0,

RE::SyncAnalysis: 2025-09-24 13:04:36 880775270 ns [0, Main] (3561) "tsDeviceExttsCorrectionNs": -434

RE::SyncAnalysis: 2025-09-24 13:04:36 880797960 ns [0, Main] (3561) }

RE::SyncAnalysis: 2025-09-24 13:04:36 880817890 ns [0, Main] (3561) ],

RE::SyncAnalysis: 2025-09-24 13:04:36 880837470 ns [0, Main] (3561) "charDevice": "/dev/rsmu0",

RE::SyncAnalysis: 2025-09-24 13:04:36 880858230 ns [0, Main] (3561) "phaseSnapDelaySeconds": 3,