System Requirements¶

Host System Hardware¶

- Hardware Debug Connection

Note

At this time it is not recommended to run cs_server natively on the SmartLynq+ module!

Host System Software¶

Operating System: please refer to Vivado Design Suite User Guide

2023.1 or newer Xilinx Hardware Server

hw_server2023.1 or newer Xilinx ChipScope Server

cs_serverPython 3.8 or newer

ChipScoPy Python Package

ChipScoPy Examples

Note

Please see ChipScoPy Installation for a complete guide to installation.

Network Considerations¶

While hw_server, cs_server, and ChipScoPy can be connected over TCP/IP networks for enhanced flexibility, it is not

recommended that they span large WANs. This can introduce performance issues. Specifically using them over VPN may have

undesirable results.

For best results all servers should be on a local physical LAN, contact your network administrator if you have questions.

Supported Versal-Based Boards¶

The example designs distributed with ChipScoPy are supported for these hardware boards:

Note

Not all examples will be supported on all hardware platforms–due to differences in the silicon.

- VCK190 (Versal AI Core Series Evaluation Board):

Versal VC1902 Device

- VMK180 (Versal Prime Series Evaluation Board):

Versal VM1802 Device

- VPK120 (Versal Premium Series Evaluation Board):

Versal VP1202 Device

User Designs¶

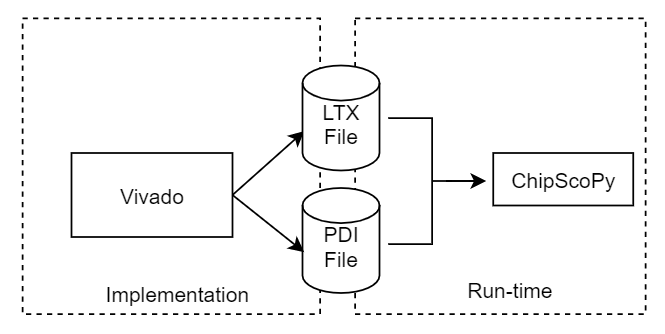

ChipScoPy supports user-generated designs targeting any Versal series device. To interact with a user design, first supply the PDI and LTX files to the programming and discovery routines.

The standard design flow will produce these output products for user-generated projects.

Vivado Design Flow¶

Note

Certain examples may also require the “hardware hand-off” file or <project_name>.hwh from the user-generated

project.