### Runtime-First FPGA Interchange Routing Contest @ ISFPGA'24

Eddie Hung, Chris Lavin, Zak Nafziger, Alireza Kaviani

4 March 2024

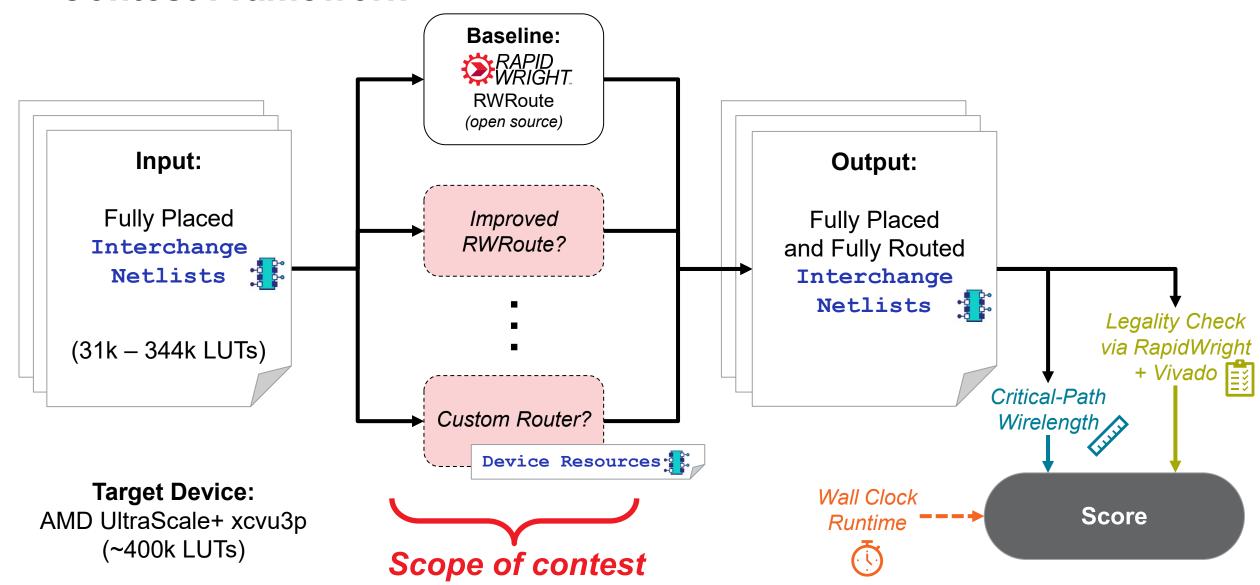

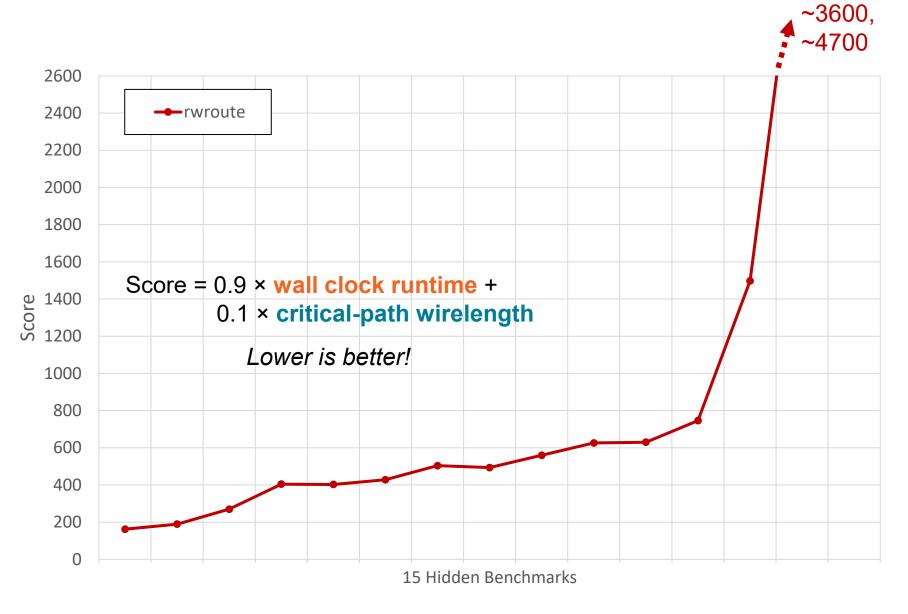

## How quickly can we route a real FPGA design if we pull out all the stops?

## How quickly can we route a real FPGA design if we pull out all the stops?

Behind legality, make runtime the top priority (ahead of timing)

## How quickly can we route a real FPGA design if we pull out all the stops?

Behind legality, make runtime the top priority (ahead of timing)

#### Goals

- 1. Demonstrate utility and efficiency of the FPGA Interchange Format

- 2. Encourage innovation into FPGA backend (place-and-route) problems

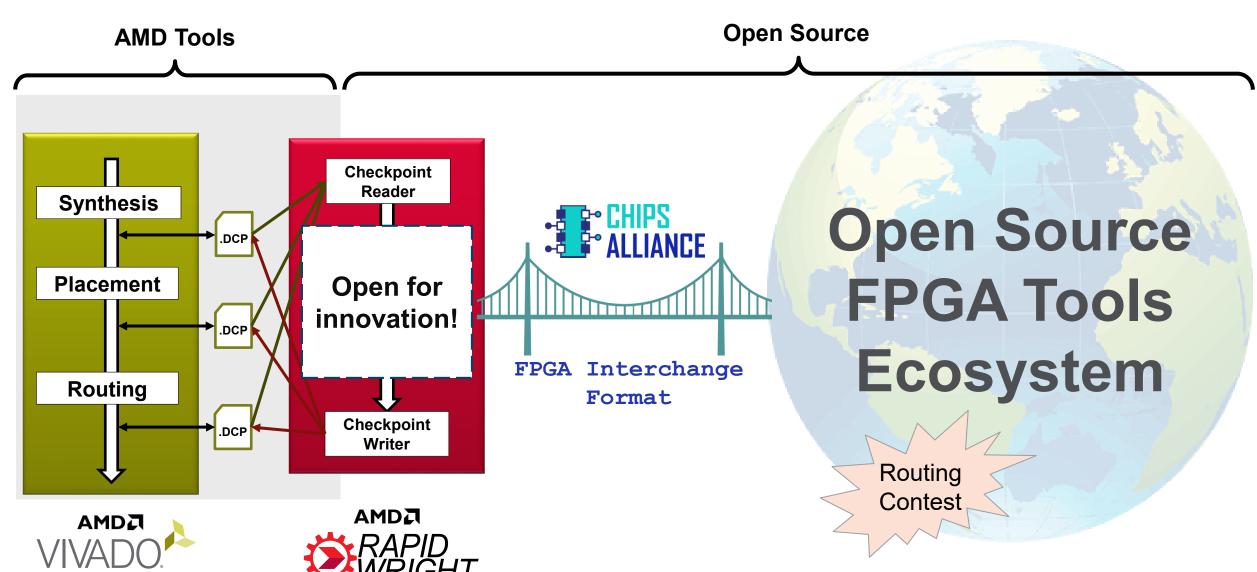

#### FPGA Interchange Format: "IR" for Backend Implementation

- Everything you need to build your own router for real devices

- (And placer, too!)

Allows the efficient exchange of design data, even at industrial scales

A vendor neutral, open source format

#### FPGA Interchange: Building a Bridge to the FPGA Backend

#### **Contest Framework**

#### **Contest Statistics**

#### **Top 5 Teams (Alphabetical Order)**

- AceRoute (Peking University/DeePoly Technology)

- Ziyun Zhang, Xinming Wei, Sunan Zou, Jiaxi Zhang, Ping Fan; Advisor: Guojie Luo

- Team Cuckoo (Peking University)

- Jiarui Wang, Xun Jiang, Chunyuan Zhao; Advisor: Yibo Lin

- CUFR (The Chinese University of Hong Kong)

- Xinshi Zang, Wenhao Lin, Shiju Lin, Qin Luo; Advisor: Evangeline F.Y. Young

- GRoute (University of Guelph)

- Dani Maarouf, Timothy Martin, Charlotte Barnes; Advisors: Shawki Areibi, Gary Grewal

- Hao<sup>3</sup> (University of Science and Technology of China)

- Wenbin Teng, Qianyu Cheng, Zhendong Zheng, Binze Jiang, Yixuan Zhu, Zihan Wang Advisors: Teng Wang, Chao Wang

### Runtime-First FPGA Interchange Routing Contest @ ISFPGA'24

Results

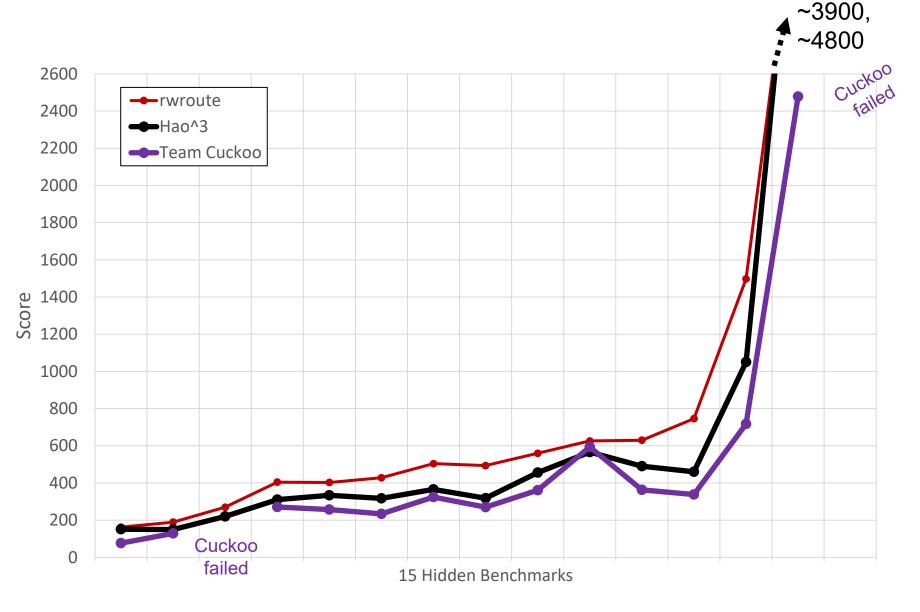

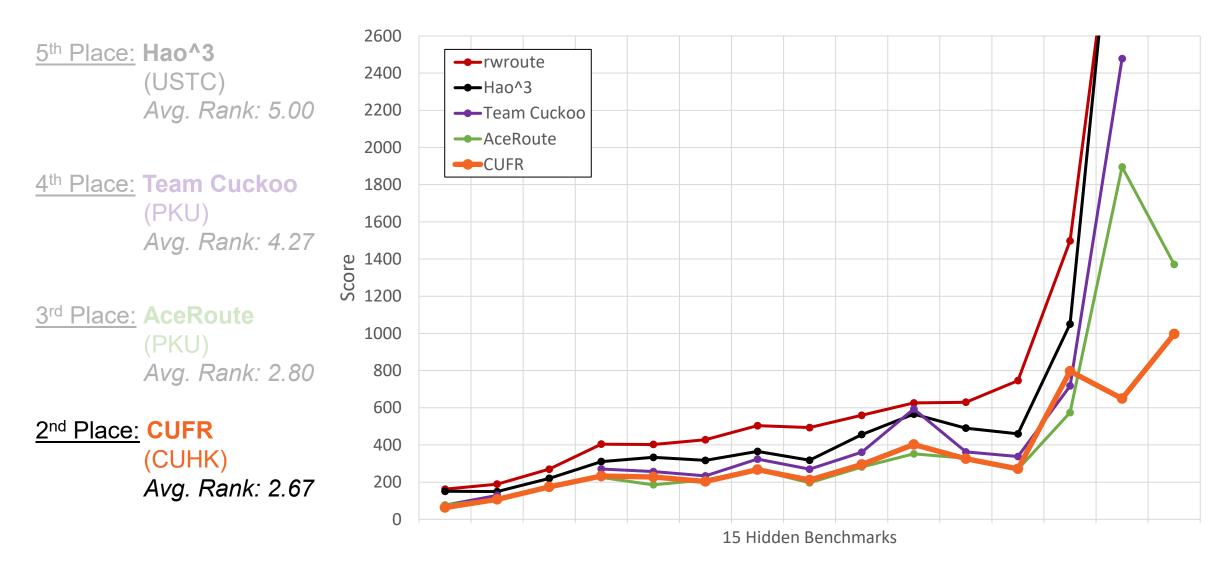

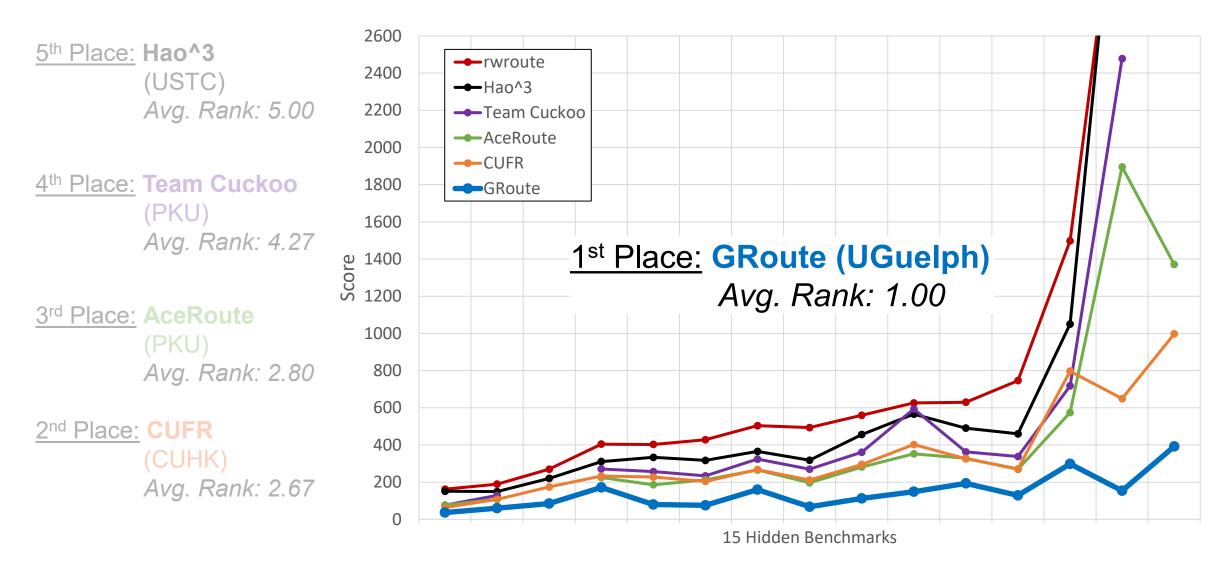

5th Place: Hao^3

(USTC)

Avg. Rank: 5.00

4th Place: Team Cuckoo

(PKU)

Avg. Rank: 4.27

5<sup>th</sup> Place: Hao^3

(USTC)

Avg. Rank: 5.00

4<sup>th</sup> Place: Team Cuckoo

(PKU)

Avg. Rank: 4.27

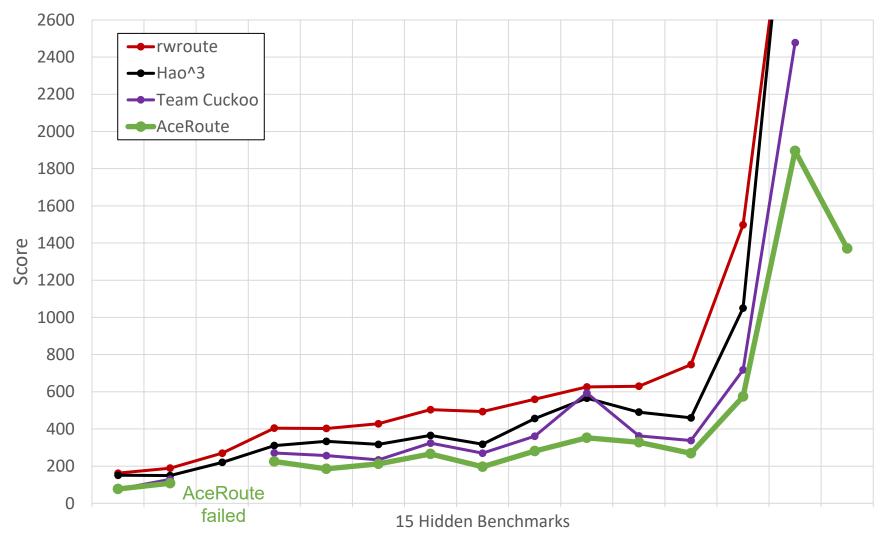

3<sup>rd</sup> Place: AceRoute

(PKU)

Avg. Rank: 2.80

#### **Behind The Scenes**

- All PathFinder (1995) based!

- 2 teams improve on RWRoute

- 3 teams built a custom router

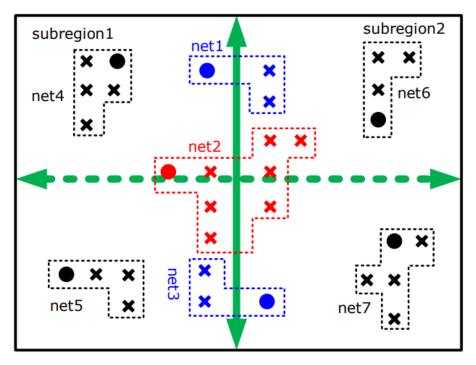

- Parallelism through:

- Recursive bi-partitioning of device

- Bounding box aware parallel scheduling

- More:

- Tolerate overlaps initially (GRoute)

- Hybrid update of congestion coefficients (CUFR)

- Bidirectional A\* search (AceRoute)

- Details on contest website

(figure from AceRoute slide)

#### **Final Thoughts**

- More room for improvement: leverage GPU acceleration!

- · Honorable mention: Daniel Kluss (Archeo Futurus) -- used all four GPUs; didn't finish by deadline

- Hidden benchmark suite will be released

- 1 slide summary and short videos with more details from top 5 teams:

https://xilinx.github.io/fpga24 routing contest

Thank you to all contest participants!!

#### **Acknowledgements**

- ISFPGA Organizers (in particular Zhiru Zhang, Aman Arora)

- AMD University Program (Mario Ruiz Noguera, Joshua Lu, Naveen Purushotham, Cathal McCabe, Hugo Andrade)

- Manages the Heterogeneous Accelerated Compute Clusters (HACC)

- AMD RAD (Nicholas Fraser, Jakoba Petri-Koenig, Thomas Preusser)

- AMD AECG (Ismail Bustany)

- Shashwat Shrivastava (EPFL)

- HACC administrators at ETH Zurich, Paderborn University, National University of Singapore

#### **COPYRIGHT AND DISCLAIMER**

©2024 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate releases, for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

THIS INFORMATION IS PROVIDED 'AS IS." AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS, OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY RELIANCE, DIRECT, INDIRECT, SPECIAL, OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# AMDI