DSP Library Lab

Introduction

Goal

- Use the DSP Vitis Libraries for the AI Engine

Design Overview

AI Engine Kernels

For the AI Engine kernel we will use the FFT/iFFT as well as the single rate, symmetrical FIR filter from the DSP Libraries.

The templated parameters for the 1D FFT are defined here

The templated parameters for the symmetrical FIR filter are defined here

Steps

This lab will make use of Makefile files to automate the building process.

AIE Engine Graph

The FFT kernel depends in the Vitis Library repository.

-

Make sure Vitis Libraries repository is downloaded

cd $HOME/xup_aie_training/ git submodule init && git submodule update -

Navigate to the

$HOME/xup_aie_training/sources/dsplib_lab/aiefolder and run makecd $HOME/xup_aie_training/sources/dsplib_lab/aie makeThe

aiecompilerwill be called to generate thelibadf.afile. This process takes around 5 minutes.Note: you can run

make -nto see what command will be run without actually executing anything -

Analyze the compilation results

vitis_analyzer build.hw/work/graph.aiecompile_summary -

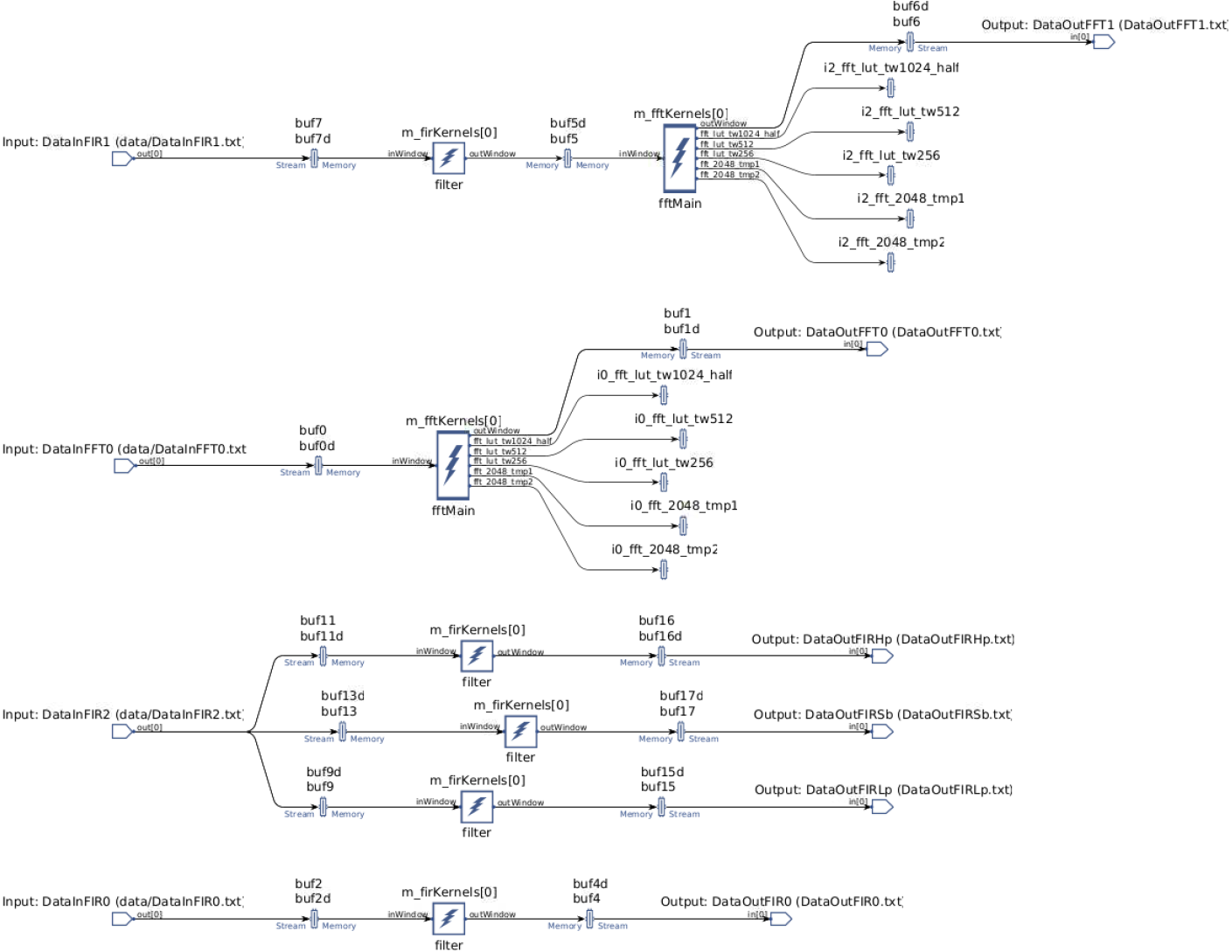

In Vitis Analyzer, open the Graph tab

Note that the Flat view is used

-

Questions for the reader by just looking at the information on Vitis Analyzer

-

Q1: How many

input_pliodoes the graph have? -

Q2: How many

output_pliodoes the graph have? -

Q3: How many instances of the

xf::dsp::aie::fir::sr_sym::fir_sr_sym_graphdoes the graph have? -

Q4: How many instances of the

xf::dsp::aie::fft::dit_1ch::fft_ifft_dit_1ch_graphdoes the graph have? -

Q5: One

input_plioport is broadcasted, how many kernels are connected to it? -

Q6: How many subgraphs are within the main graph?

-

Q7: How many Tiles are used for AIE Kernels?

-

Q8: How many Tiles are used for Buffers?

-

Q9: How many Tiles are used for Stream Interconnect?

-

-

Explore the files in the directory

$HOME/xup_aie_training/sources/dsplib_lab/aie/src/-

fft.hppdeclares a graphFFT1d_graphwhich instantiates the FFT functionxf::dsp::aie::fft::dit_1ch::fft_ifft_dit_1ch_graph -

fir.hppdeclares a graphFIR_129_symwhich instantiates the FIR functionxf::dsp::aie::fir::sr_sym::fir_sr_sym_graphit also declares four different set of taps. Note as we are using a symmetrical filter we only need to declare half of the coefficients plus the central tap -

graph.hppdeclares the main graphDSPLibGraph. There is also the declaration ofSpectrumGraph, which connects an fir with an fft instance. Finally, the declaration ofMultiFIRGraphwhich instantiates threeFIR_129_symgraph an initializes the tap values via an initialization list -

graph.cppdefines the emulation environment

In an AMD preconfigured instance you can run

code $HOME/xup_aie_training/sources/dsplib_lab/aie/src/to open the files with VS Code -

Run AIE Emulation

-

Run the AIE Emulation by executing the following code on the command line:

make aieemuThis AIE emulation takes around 3 minutes.

Note: the AIE output results are not being checked

-

Visualize the emulation reports by running

vitis_analyzer build.hw/aiesimulator_output/default.aierun_summary -

Questions for the reader by just looking at the information on Vitis Analyzer

-

Q10: How many cycle does one instance of the FIR takes to complete?

-

Q11: How many cycle does one instance of the FTT takes to complete?

-

Modify the Cascade Length

In this part we are going to modify the cascade length for both the FFT and FIR instances and see the changes in the graph and performance.

In an AMD preconfigured instance you can run code $HOME/xup_aie_training/sources/dsplib_lab/aie/src/ to open the files with VS Code

-

Open the file

$HOME/xup_aie_training/sources/dsplib_lab/aie/src/fir.hppand change the macroFIR129_CASCADE_LENto#define FIR129_CASCADE_LEN 2 -

Open the file

$HOME/xup_aie_training/sources/dsplib_lab/aie/src/fft.hppand change the macroFFT_CASCADE_LENto#define FFT_CASCADE_LEN 2 -

Save previous compilation results

cd $HOME/xup_aie_training/sources/dsplib_lab/aie mv build.hw/ build_no_cascade.hw/ -

Recompile the AIE code

cd $HOME/xup_aie_training/sources/dsplib_lab/aie make -

Analyze the compilation results

vitis_analyzer build.hw/work/graph.aiecompile_summary -

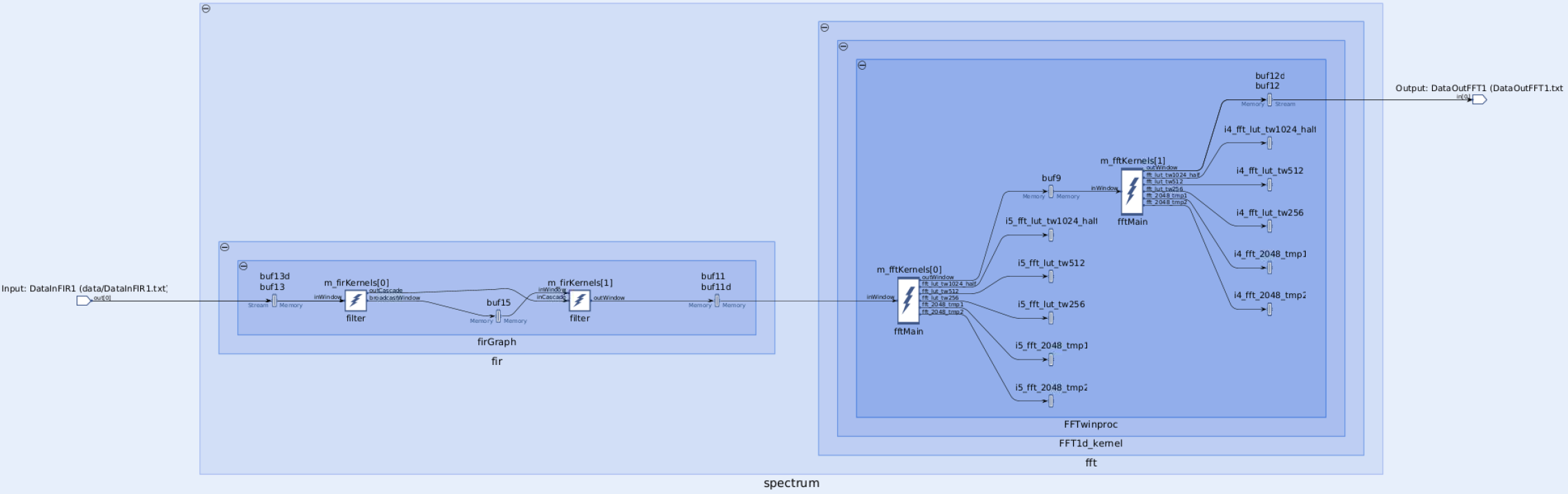

In Vitis Analyzer, open the Graph tab

Note only a portion of the graph is shown.

From this view, you can see that now the FIR instance is split in two kernels, which communicate using both a cascade interface and a buffer. Whereas, the FFT instance is also split in two kernels and these two kernels communicate using only a buffer.

Run AIE Emulation for Cascaded Kernels

-

Run the AIE Emulation by executing the following code on the command line:

make aieemuThis AIE emulation takes around 3 minutes.

Note: the AIE output results are not being checked

-

Visualize the emulation reports by running

vitis_analyzer build.hw/aiesimulator_output/default.aierun_summary -

Questions for the reader by just looking at the information on Vitis Analyzer

-

Q12: How many cycle does one instance of the FIR takes to complete?

-

Q13: How many cycle does one instance of the FTT takes to complete?

-

Assignments for the Reader

The following assignments are optional, however they will help deepen your knowledge about the DSP Libraries. No solution is provided for these assignments.

-

Use the Matrix Multiply from the DSPLib, add to the graph an instance of

xf::dsp::aie::blas::matrix_mult::matrix_mult_graphusing one of the real datatypesReview the documentation of this library here

-

Implement a decimation symmetric FIR filter, add to the graph an instance of

dsplib::fir::decimate_sym::fir_decimate_sym_graphusing one of the real datatypesReview the documentation of this library here

-

For the existing FIR filters use streaming interface instead of window interface

Review the documentation of this library here

-

Design your own single rate, asymmetrical filter.

For this, you will have to compute the coefficients and call the appropriate function

If you are attending an in-person tutorial, you can request support from your instructor. Otherwise, open a GitHub issue

Appendix

Answers

-

Q1: The graph has four

input_plio -

Q2: The graph has six

output_plio -

Q3: The graph has five

xf::dsp::aie::fir::sr_sym::fir_sr_sym_graphinstances -

Q4: The graph has two

xf::dsp::aie::fft::dit_1ch::fft_ifft_dit_1ch_graphinstances -

Q5: The input

input_plioportDataInFIR2is broadcasted to three instances ofxf::dsp::aie::fir::sr_sym::fir_sr_sym_graph -

Q6: There are two subgraphs:

SpectrumGraphandMultiFIRGraph. Thefftandfirgraph are subgraph but not defined by our code -

Q7: 7 tiles are used for AIE Kernels

-

Q8: 15 tiles are used for Buffers

-

Q9: 19 Tiles are used for Stream Interconnect?

-

Q10: Looking at the Profile tab, the function

filtertakes ~ 11,183 cycles -

Q11: Looking at the Profile tab, the function

fftMaintakes ~ 3,411 cycles -

Q12: With a cascade length of 2, the FIR is split into two kernels one

filterinstance takes ~ 7,336 cycles whereas the another takes ~ 8,7510 cycles. Bare in mind, that these two instances run in parallel -

Q13: With a cascade length of 2, the FFT is split into two kernels one

fftMaininstance takes ~ 1,785 cycles whereas the another takes ~ 1,657 cycles. Bare in mind, that these two instances run in parallel

Copyright© 2023 Advanced Micro Devices