Presentations

Vitis

| Title | YouTube Link | PDF Link |

|---|---|---|

| Xilinx Platforms Introduction |  Xilinx Platforms Introduction Xilinx Platforms Introduction |

|

| Intro to Vitis for Acceleration Platforms |  Intro to Vitis for Acceleration Platforms Intro to Vitis for Acceleration Platforms |

|

| Vitis Tool Flow |  Vitis Tool Flow Vitis Tool Flow |

|

| Open CL Execution Model |  Open CL Execution Model Open CL Execution Model |

|

| Vitis Design Analysis |  Vitis Design Analysis Vitis Design Analysis |

|

| Vitis Design Methodology |  Vitis Design Methodology Vitis Design Methodology |

|

| Host Code Optimization |  Host Code Optimization Host Code Optimization |

|

| Kernel Optimization |  Kernel Optimization Kernel Optimization |

|

| Vitis Accelerated Libraries |  Vitis Accelerated Libraries Vitis Accelerated Libraries |

|

| Vitis hardware debug |  |

|

| Vitis RTL kernels Accelerated Libraries |  |

PYNQ

PYNQ introduction, and short lab companion videos that cover topics that are not addressed in the main presentation. We recommend watching the lab while doing the PYNQ labs.

| Title | YouTube Link |

|---|---|

| PYNQ for Compute Acceleration |  PYNQ for Compute Acceleration PYNQ for Compute Acceleration |

| Lab: Using Multiple Devices |  Lab: Using Multiple Devices Lab: Using Multiple Devices |

| Lab: Hardware Emulation |  Lab: Hardware Emulation Lab: Hardware Emulation |

| Lab: Packaging Your Designs |  Lab: Packaging Your Designs Lab: Packaging Your Designs |

Overview of the Vitis flow

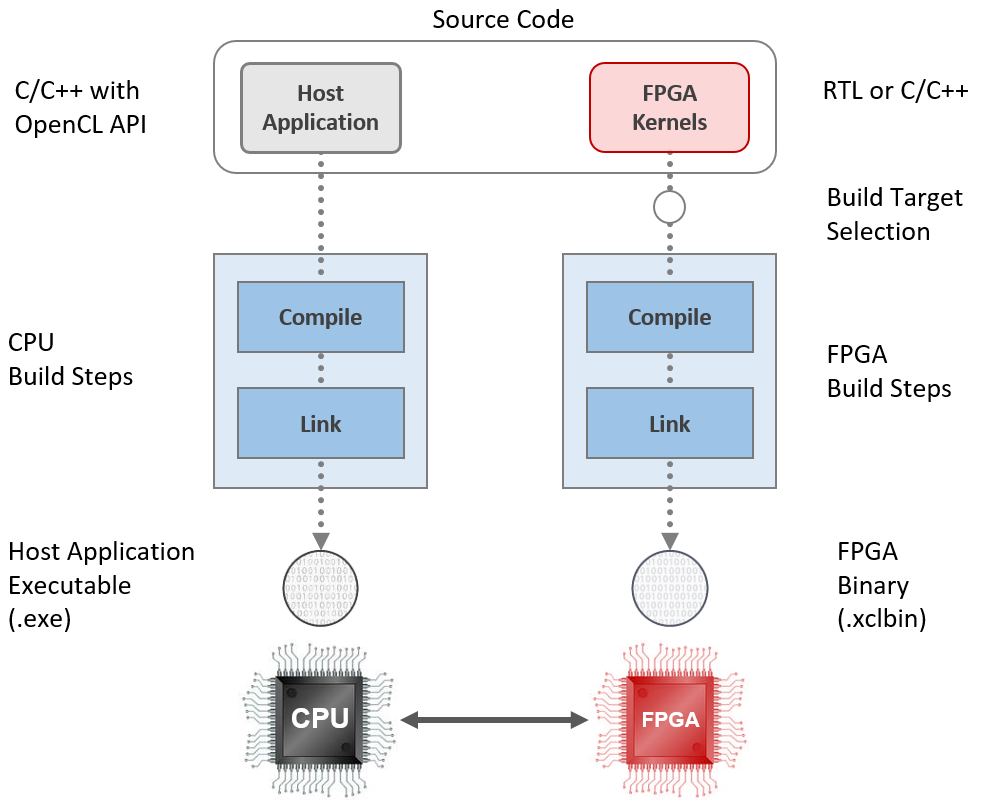

- Vitis is the development environment used to create host applications and hardware accelerators. It includes host CPU and FPGA compilers as well as profiling and debugging tools

- In Vitis, the host application can be written in C or C++ and uses the OpenCL API or the XRT (Xilinx Runtime Library) to interact with the accelerated hardware functions running on the FPGA. The accelerated hardware functions (also referred to as ‘hardware kernels’, or just ‘kernels’) can be written in C, C++, OpenCL or RTL

Copyright© 2021 Xilinx