AIE Test Harness¶

This repository provides a test harness to help AIE developers easily build and test their AIE graph on VCK190 boards. This test harness is designed to provide a very simple and intuitive transition from the AIE simulation environment to testing on hardware. With the test harness, AIE graphs running in simulation can be taken to hardware in just a few minutes and with only a few minor modifications.

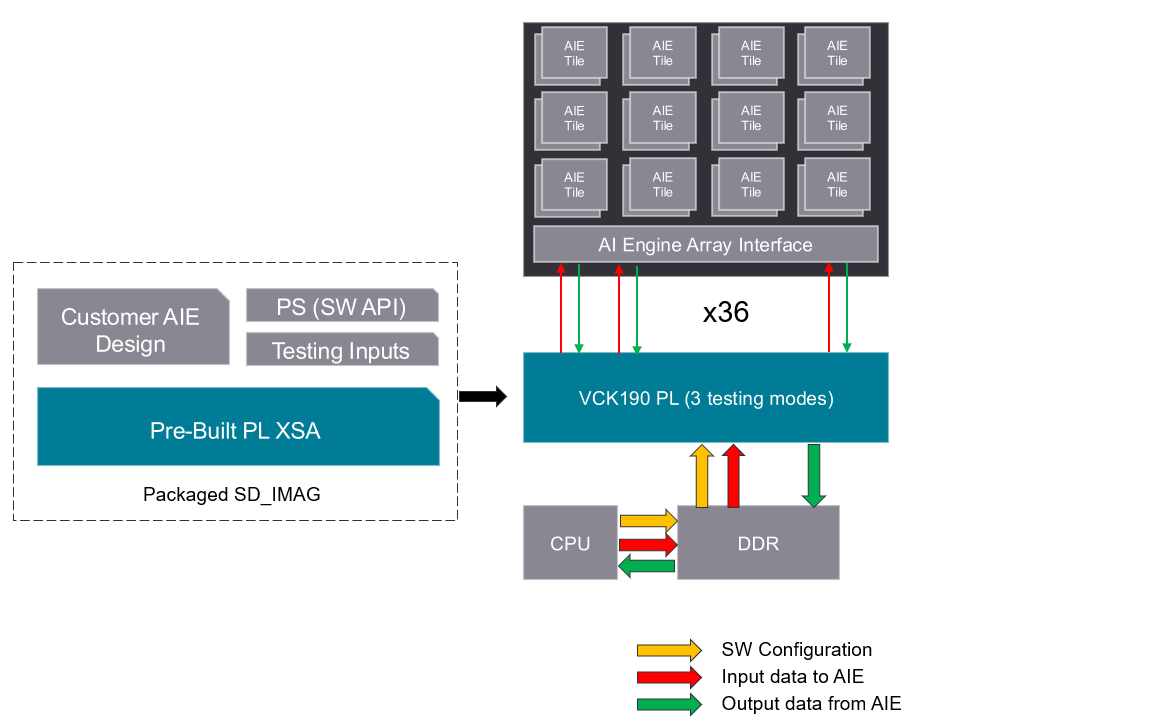

The test harness consists of three main elements:

- A precompiled .xsa implementing a DMA engine to transfer data between DDR and a set of predefined AI Engine PLIOs.

- A set of software APIs to facilitate the development of the application used to initialize the device and run the tests.

- A script to easily package the user’s libadf.a and test application, and generate the boot image for VCK190.

The test harness leverages a precompiled .xsa file which is used as an input platform when compiling the AIE graph. This allows skipping the v++ link step after compiling the libadf.a and directly go to the v++ package step to generate the hardware boot image. This saves the most time-consuming part of the build process for on-board tests and allows for fast and predictable iterations.

The precompiled .xsa implements a DMA engine with 72 channels. 36 channels send data from DDR to AIE and 36 send data from AIE to DDR. The DMA engine is designed to allow maximum throughput on the PLIO interfaces, ensuring that the AIE graph isn’t artificially stalled by the DMA channels and thereby allowing accurate performance testing in hardware.

The software APIs enable to easily build SW applications to test an AIE graph using the test harness. The APIs are designed to structure test applications following these 5 simple steps:

- Initialize the device and load the xclbin

- Configure how each DMA channel with transfer data to or from the AIE graph

- Run the AIE graph

- Wait for all the data to be received

- Check correctness of results and performance for each channel