Embedded Designs¶

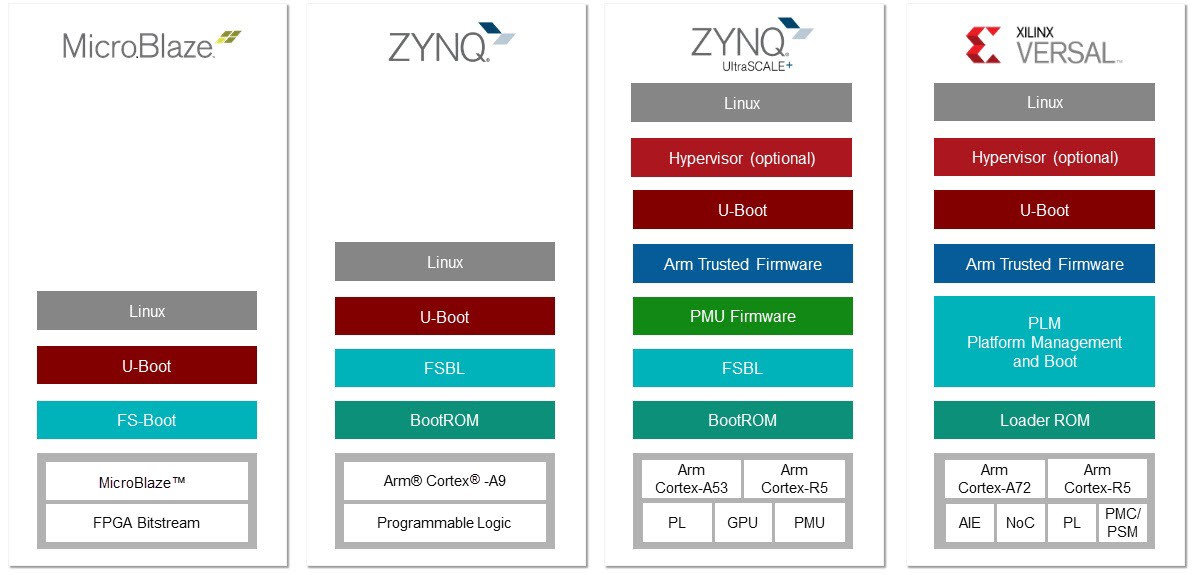

Xilinx and its Ecosystem Partners deliver embedded tools and runtime environments designed to enable you to efficiently and quickly move from concept to release. We provide you with all the components needed to create your embedded system using Xilinx Zynq® SoC and Zynq UltraScale+ MPSoC devices, MicroBlaze™ processor cores, and Arm Cortex-M1/M3 micro controllers including open source operating systems and bare metal drivers, multiple runtimes and Multi-OS environments, sophisticated Integrated Development Environments, and compilers, debuggers, and profiling tools.

This repository provides information about creating embedded designs. The following documents are available.

Introduction¶

Tutorial |

Board |

Description |

|---|---|---|

Versal VMK180/VCK190 |

Provides an introduction for using the Xilinx® Vivado® Design Suite flow and the Vitis™ unified software platform for embedded development on a Versal™ VMK180/VCK190 evaluation board. |

|

ZCU102 Rev 1.0/1.1 |

Provides an introduction to using the Xilinx Vivado Design Suite flow and the Vitis unified software platform for embedded development on a Zynq UltraScale+ MPSoC device. |

|

ZC702 Rev 1.0 |

Provides an introduction to using the Xilinx Vivado Design Suite flow and the Vitis unified software platform for embedded development on a Zynq-7000 SoC device. |

Feature Tutorials¶

Tutorial |

Description |

|---|---|

First Stage Boot Loader (FSBL) can initialize the SoC device, load the required application or data to memory, and launch applications on the target CPU core. An FSBL is provided in the Vitis platform project (if you enabled creating boot components while creating the platform project), but you are free to create additional FSBL applications as general applications for further modification or debugging purposes. |

|

Enable profiling features for the standalone domain or board support package (BSP) and the application related to AXI CDMA, which you created in Linux Booting and Debug in the Vitis Software Platform. |

Design Tutorials¶

Tutorial |

Description |

|---|---|

Example Setup for a Graphics and DisplayPort Based Sub-System |

Demonstrates the configurations, packages, and tool flow required for running designs based on GPU and DP on a Zynq UltraScale+ MPSoC device. |

Debugging¶

Tutorial |

Description |

|---|---|

Provides specific examples of embedded software debug situations and explains how the various Xilinx debug features can help. |

User Guides¶

Tutorial |

Description |

|---|---|

Vitis Unified Software Platform User Guide System Performance Analysis |

Describes the technical details of the performance analysis toolbox, as well as a methodology explaining its usefulness and depth. |

Provides step-by-step instructions for generating a reference design for the Dhrystone benchmark and building and running the Dhrystone application. |