RTL モジュール: AES¶

AES 暗号化アルゴリズムの概要¶

AES アルゴリズムは、一般的に使用される対称キー暗号化アルゴリズムで、データの暗号化と復号化の両方に同じキーが使用されます。AES アルゴリズムの入力および出力データ ブロックは、16 バイト ブロック (128 ビット) です。AES のキーの長さには、128 ビット、192 ビット、256 ビットの 3 種類あります。AES 暗号化および暗号化操作を実行する前に、キーが指定されたときにキー拡張と呼ばれる操作を実行する必要があります。AES アルゴリズムには、ビット単位およびバイト単位の演算が多数含まれているため、ハードウェア アクセラレータを使用してインプリメントするのに非常に適しています。

アプリケーションでは、AES には広く使用されている 5 つの使用モデルがあります。

電子コードブック (ECB)

暗号ブロック連鎖 (CBC)

暗号フィードバック (CFB)

出力フィードバック (OFB)

カウンター (CTR)

このチュートリアルでは、ECB と CBC のみを使用します。次の図は、これらのモデルについて説明しています。注記: 図は、ウィキペディア (wikipedia.org) からのものです。

AES-ECB 暗号化¶

AES-ECB 復号化¶

AES-CBC 暗号化¶

AES-CBC 復号化¶

RTL モジュール AES¶

RTL モジュール Aes は、AES 暗号化/復号化モジュールのコア モジュールです。ネイティブ RTL ポート インターフェイスを使用します。Verilog ソース コードは ~/aes/rtl ディレクトリにあります。信号の説明は次のとおりです。

| 名前 | 幅 (ビット) | 方向 | 内容 |

|---|---|---|---|

| CLK | 1 | in | クロック入力 |

| RESETn | 1 | in | アクティブ Low のリセット入力 |

| DATA_INPUT | 128 | in | 暗号化または復号化用の入力データ ブロック |

| KEY | 256 | in | 128/192 ビットキー使用時、MSB にアライメントした場合の暗号化または復号化のための AES キー (0 を LSB に補足) |

| DATA_OUTPUT | 128 | out | 暗号化または復号化用の出力データ ブロック |

| NK | 2 | in | AES キーの長さ: 2'b00 = 128 ビット、2'b01 = 192 ビット、2'b10 = 256 ビット |

| NR | 4 | in | 予約済み、一般的な AES 操作用に 4'b0000 に接続 |

| START_CIPHER | 1 | in | 1 サイクルのアクティブ High トリガーを指定した場合、暗号化動作 (暗号化または復号化) 実行 |

| START_KEYEXP | 1 | in | 1 サイクルのアクティブ High トリガーを指定した場合、AES キー拡張操作実行 |

| OP_FINISH | 1 | out | 暗号化または復号化ジョブが実行中の場合、OP_FINISH は Low のまま。OP_FINISH はアイドル状態で High のまま。 |

| EXP_FINISH | 1 | 出力 | キー拡張ジョブが実行中の場合、EXP_FINISH は Low のまま。EXP_FINISH は、アイドル状態で High のまま。 |

テストベンチ¶

単純なネイティブ Verilog テストベンチは、~/aes/tbench ディレクトリにあります。テストベンチは、Perl スクリプトによって生成されたランダム データセットをスティミュラスとして使用し、出力結果を OpenSSL ユーティリティによって生成された基準データセットと比較します。~/aes/runsim_aes_xsim.sh シェル スクリプトを使用して、入力スティミュラスと出力基準を生成し、Vivado XSim でシミュレーションを実行します。

使用方法¶

シミュレーションを実行する makefile が提供されています。次のコマンドを使用して、Verilog シミュレーションを実行します。

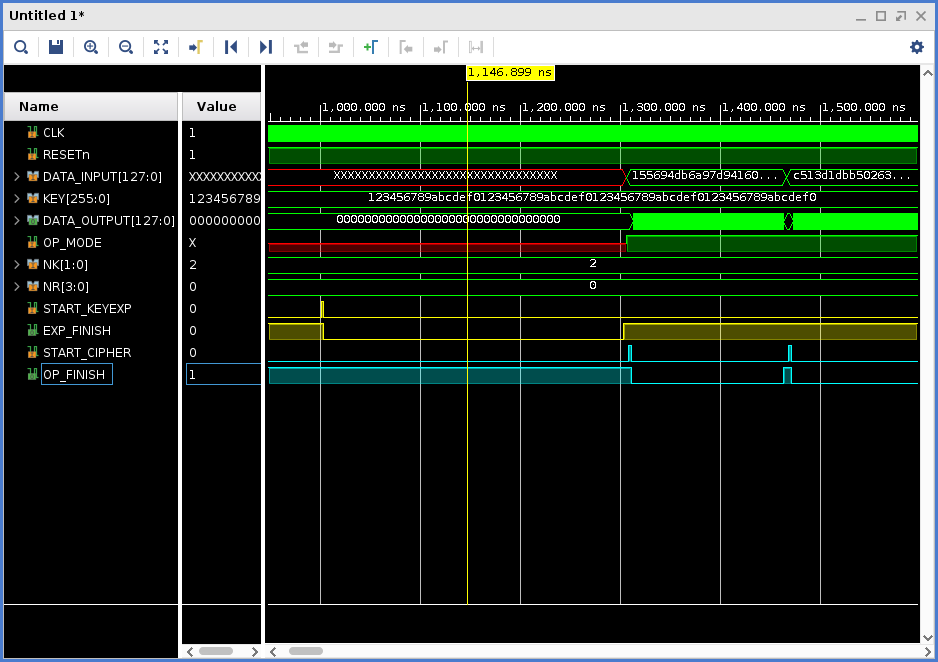

cd ~/aes make runsim シミュレーションは、256 の入力ワード (128 ビット) と事前定義された KEY で実行されます。~/aes/aes runsim_aes_xsim.sh ファイルでシミュレーション オプションを変更できます。シミュレーションが完了すると、work.tb_aes.wdb 波形ダンプ ファイルが生成され、インターフェイス波形を確認できるようになります。次の図は、インターフェイス波形の例を示しています。

ここまでで AES モジュールに関する必要な情報が取得できたので、必要な AXI インターフェイスと IP を追加して、Vitis フローで使用可能なカーネルにできるようになりました。これについては、次のセクションの「RTL カーネル: krnl_aes」で説明します。