2021.2 Vitis™ アプリケーション アクセラレーション チュートリアル2020.2 チュートリアルを参照 |

1.Vitis HLS プロジェクトの作成¶

Vitis HLS ツールでは、C/C++ コードを指定して Vitis コア開発キット カーネル (.xo) または RTL IP に合成し、ザイリンクス デバイスの PL 領域にインプリメンテーションできるようします。新規プロジェクトを作成するには、まず合成する C/C++ ソース コードを特定します。

このチュートリアルでは、値の入力行列を処理して、固定係数を適用し、変更された値の行列を戻す単純な離散コサイン変換 (DCT) アルゴリズムを使用します。最上位 DCT 関数は、reference_files/src フォルダーの dct.cpp に含まれます。

次のコマンドを入力して、Vitis HLS を GUI モードで起動します。

vitis_hlsVitis HLS が開きます。

[File] → [New Project] をクリックします。

New Vitis HLS Project ウィザードが表示されます。

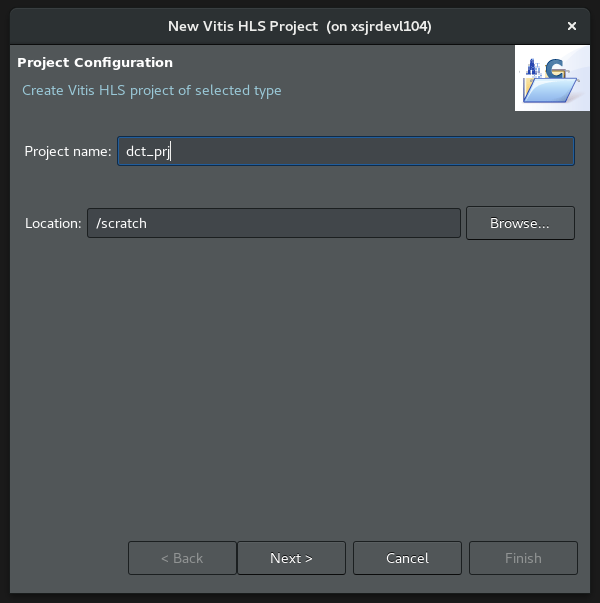

Vitis HLS プロジェクト タイプを作成します。

[Project name] フィールドに「

dct_prj」と入力します。[Location] フィールドで [Browse] をクリックし、プロジェクトのディレクトリを選択します。

[Next>] をクリックします。

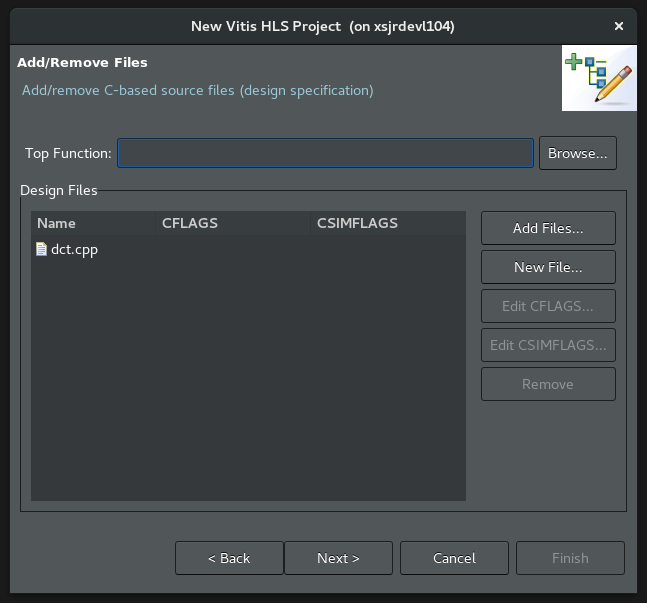

New Vitis HLS Project ウィザードの [Add/Remove Files] ページが表示されます。

次のように選択します。

[Add Files] をクリックしてプロジェクトのソースを指定します。

./reference-files/src フォルダー ディレクトリに移動して、dct.cpp を選択します。

New Vitis HLS Project ウィザードで [Top Function] フィールドの [Browse] ボタンをクリックし、[Select Top Function] ダイアログ ボックスを開きます。

dct (dct.cpp) 関数を選択して [OK] をクリックします。

![[Select Top Function] ダイアログ ボックス](../../../_images/create_project-select_top_function.png)

[Next>] をクリックします。

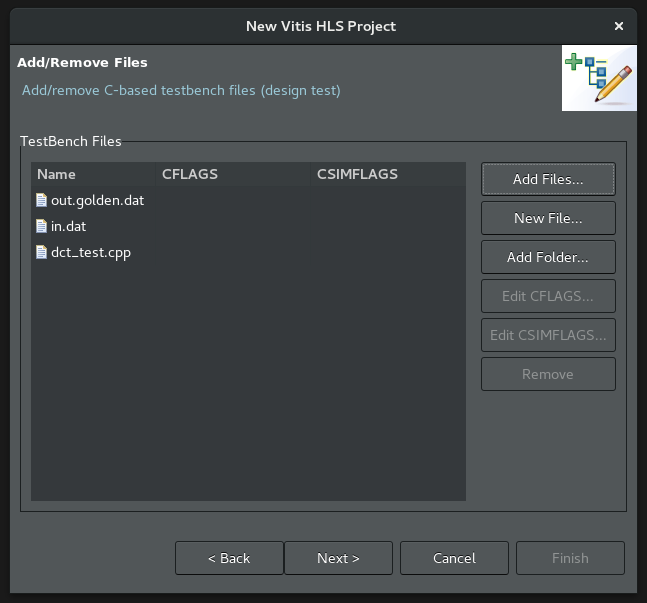

New Vitis HLS Project ウィザードの [Add/Remove Testbench Files] ページが表示されます。

適切なテストベンチを記述すると、C 関数を RTL シミュレーションよりも短時間で実行できるので、生産性が上がります。C を使用してアルゴリズムを開発して合成前に検証する方が、RTL コードを開発してデバッグするよりもはるかに高速です。詳細は、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) の Vitis HLS フローのテストベンチの記述を参照してください。

[Add Files] をクリックしてテストベンチおよびプロジェクトの追加ファイルを指定します。

./reference-files/srcフォルダーの dct_test.cpp、in.dat、および out.golden.dat を選択します。dct_test.cppはカーネルを介して複数回繰り返すデザインのテストベンチです。in.datには、カーネルで処理される入力値が含まれます。out.golden.datには、dct 関数の出力との比較に使用する既知の出力結果が含まれます。

[Next>] をクリックします。

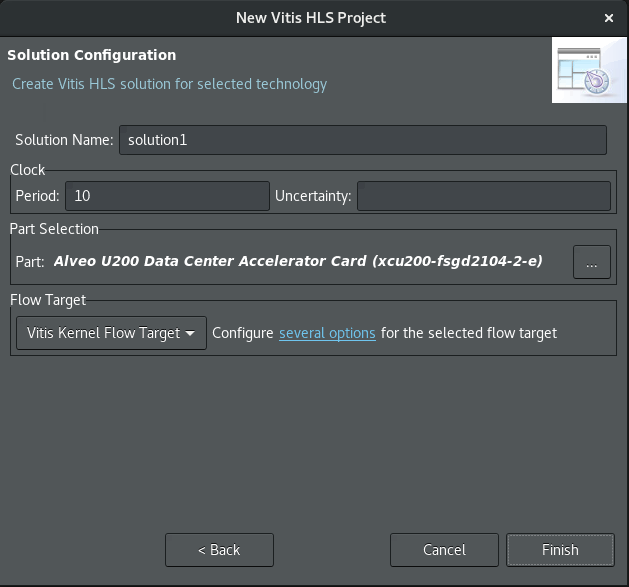

New Vitis HLS Project ウィザードの [Solution Configuration] ページが表示されます。

このページでは、ビルドに使用する特定のビルド コンフィギュレーションであるソリューションを作成および定義します。ソリューションには、クロック周波数の定義およびクロックのばらつきが含まれ、ビルドするプラットフォームとザイリンクス デバイスが指定されます。ソリューションは、RTL コードを構築し、異なるソリューションで異なる指示子を使用してさまざまな最適化をテストするためのフレームワークを提供します。

次のように選択します。

[Solution Name] を指定するか、デフォルトの名前をそのまま使用します。

[Period] でクロックの周期をデフォルトの 10 ns に指定します。

クロックのばらつきは空白のままにします。クロックのばらつきを指定しない場合、デフォルトではクロック周期の 27% に設定されます。詳細は、Vitis 統合ソフトウェア プラットフォームの資料 (UG1416) の Vitis HLS フローのクロック周波数の指定を参照してください。

[Browse] をクリックして、プロジェクトのパーツを定義します。

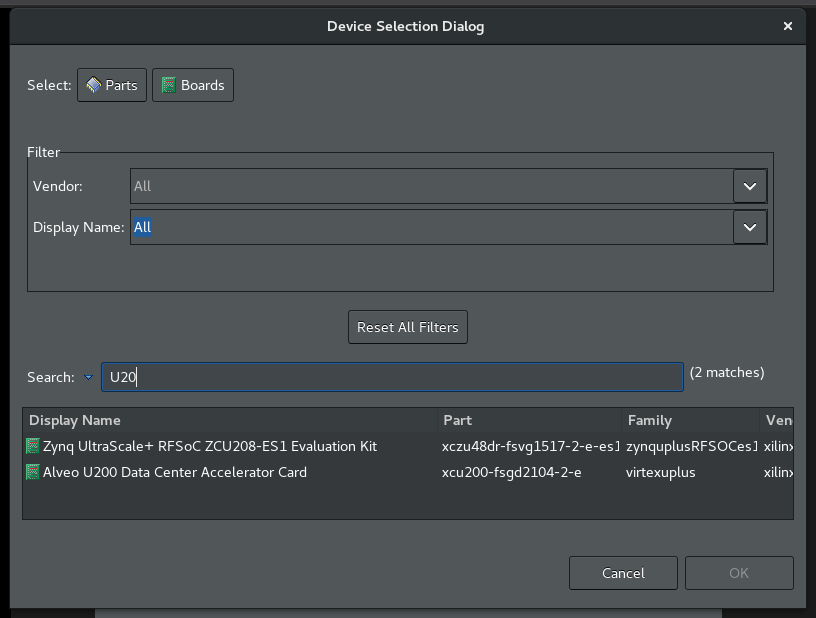

[Device Selection] ダイアログボックスが開きます ([Boards] カテゴリにデバイスが表示されます。次の手順を参照してください。

[Device Selection Dialog] ダイアログ ボックスでは、ザイリンクス デバイスを指定したり、1 つまたは複数のザイリンクス デバイスを含むボードを選択したりできます。

次のように選択します。

ダイアログ ボックス上部の [Boards] をクリックします。

[Search] フィールドに「

U200」と入力します。テキストを入力していくにつれ、選択肢が狭まっていきます。[Alveo U200 Data Center Accelerator Card] をクリックします。

[OK] をクリックします。

[New Vitis HLS Project] ダイアログ ボックスに戻ります。

[Solution Configuration] ページでドロップダウン リストターゲットから [Vitis Kernel Flow] をクリックします。

これにより、プロジェクトの出力として Vitis アプリケーション アクセラレーション ハードウェア カーネル (.xo) を作成できるようになります。Vitis カーネル フローをイネーブルにした場合のデフォルト動作については、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) の Vitis HLS フローの Vitis HLS プロセスの概要を参照してください。

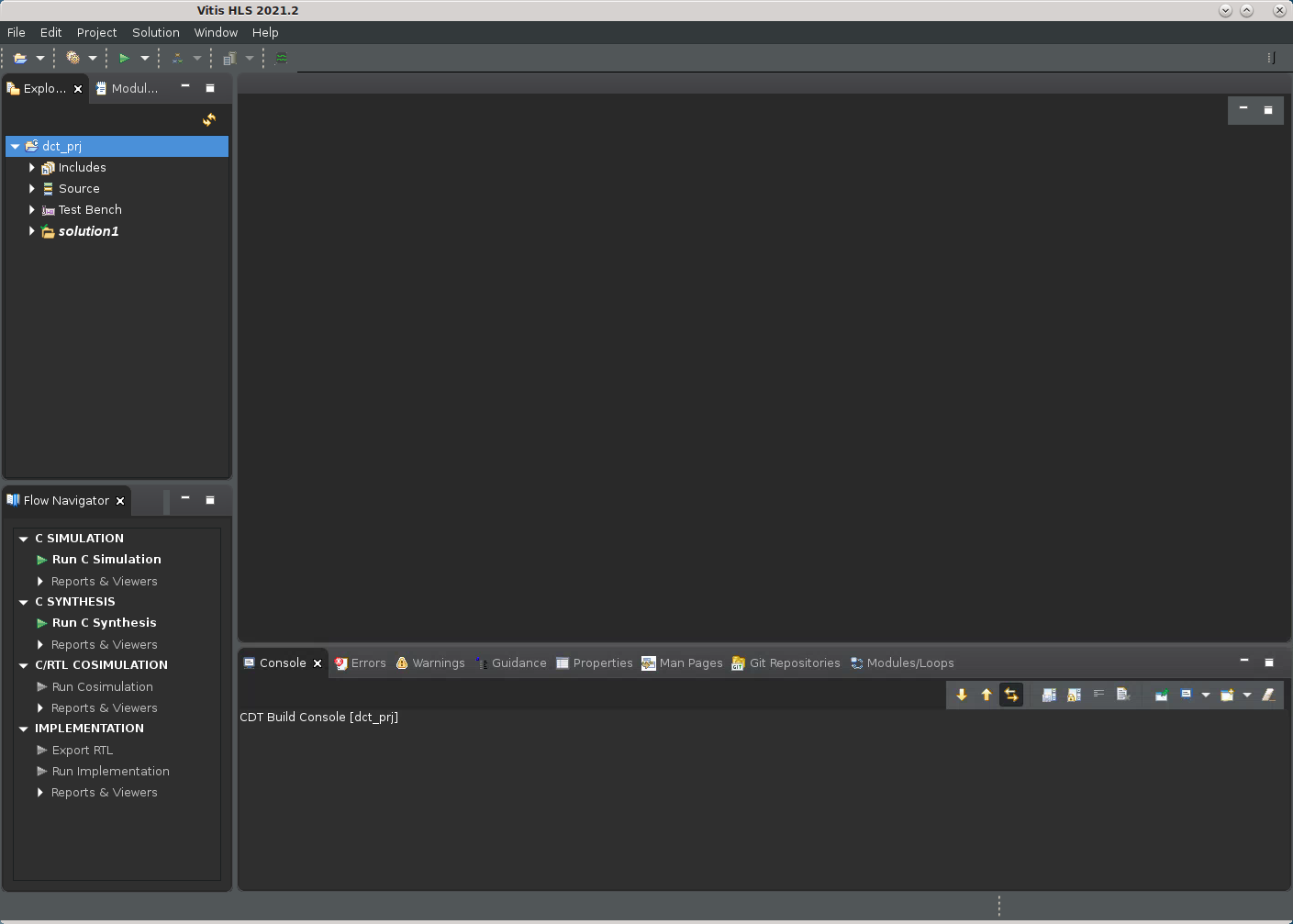

プロジェクト設定が終了したので、[Finish] をクリックします。 Vitis HLS で新規プロジェクトがデフォルト表示で開きます。

まとめ¶

DCT プロジェクトを作成し、ザイリンクス デバイスまたはボードをターゲットに指定し、ソリューション特性を設定しました。次の演習「シミュレーション、合成の実行と結果の解析」に進んでください。

Copyright© 2021 Xilinx