Overview¶

To facilitate local memory allocation on FPGA devices, the Vitis Vision

library functions are provided in templates with compile-time

parameters. Data is explicitly copied from cv::Mat to xf::cv::Mat

and is stored in physically contiguous memory to achieve the best

possible performance. After processing, the output in xf::cv::Mat is

copied back to cv::Mat to write it into the memory.

xf::cv::Mat Image Container Class¶

xf::cv::Mat is a template class that serves as a container for storing

image data and its attributes.

Note

The xf::cv::Mat image container class is similar to the cv::Mat class of the OpenCV library.

Class Definition¶

template<int T, int ROWS, int COLS, int NPC>

class Mat {

public:

unsigned char allocatedFlag; // flag to mark memory allocation in this class

int rows, cols, size; // actual image size

#ifdef __SDSVHLS__

typedef XF_TNAME(T,NPC) DATATYPE;

#else // When not being built for V-HLS

typedef struct {

XF_CTUNAME(T,NPC) chnl[XF_NPIXPERCYCLE(NPC)][XF_CHANNELS(T,NPC)];

} __attribute__ ((packed)) DATATYPE;

#endif

//#if (defined (__SDSCC__) ) || (defined (__SYNTHESIS__))

#if defined (__SYNTHESIS__) && !defined (__SDA_MEM_MAP__)

DATATYPE *data __attribute((xcl_array_geometry((ROWS)*(COLS>> (XF_BITSHIFT(NPC))))));//data[ ROWS * ( COLS >> ( XF_BITSHIFT ( NPC ) ) ) ];

#else

DATATYPE *data;

#endif

Mat(); // default constructor

Mat(Size _sz);

Mat(int _rows, int _cols);

Mat(int _size, int _rows, int _cols);

Mat(int _rows, int _cols, void *_data);

Mat(const Mat&); // copy constructor

~Mat();

Mat& operator= (const Mat&); // Assignment operator

XF_TNAME(T,NPC) read(int index);

float read_float(int index);

void write(int index, XF_TNAME(T,NPC) val);

void write_float(int index, float val);

void init (int _rows, int _cols, bool allocate=true);

void copyTo (void* fromData);

unsigned char* copyFrom ();

const int type() const;

const int depth() const;

const int channels() const;

template<int DST_T>

void convertTo (Mat<DST_T, ROWS, COLS, NPC> &dst, int otype, double alpha=1, double beta=0);

};

Parameter Descriptions

The following table lists the xf::cv::Mat class parameters and their

descriptions:

Parameter |

Description |

|---|---|

rows |

The number of rows in the image or height of the image. |

cols |

The number of columns in the image or width of the image. |

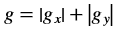

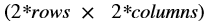

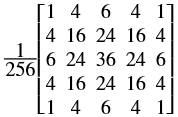

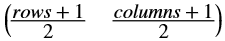

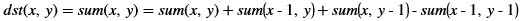

size |

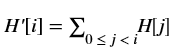

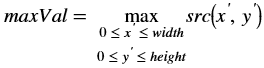

The number of words stored in the data member. The

value is calculated using

|

allocatedFlag |

Flag for memory allocation status |

*data |

class parameters and the pointer to the words that store the pixels of the image. |

The following table lists the member functions and their descriptions:

Member Functions |

Description |

|---|---|

Mat() |

This default constructor initializes the Mat object sizes, using the template parameters ROWS and COLS. |

Mat(int _rows, int _cols) |

This constructor initializes the Mat object using arguments _rows and _cols. |

Mat(const xf::cv::Mat &_src) |

This constructor helps clone a Mat object to another. New memory will be allocated for the newly created constructor. |

Mat(int _rows, int _cols, void *_data) |

This constructor initializes the Mat object using arguments _rows, _cols, and _data. The *data member of the Mat object points to the memory allocated for _data argument, when this constructor is used. No new memory is allocated for the *data member. |

convertTo(Mat <DST_T,ROWS, COLS, NPC> &dst, int otype, double alpha=1, double beta=0) |

|

copyTo(* fromData) |

Copies the data from Data pointer into physically contiguous memory allocated inside the constructor. |

copyFrom() |

Returns the pointer to the first location of the *data member. |

read(int index) |

Readout a value from a given location and return it as a packed (for multi-pixel/clock) value. |

read_float(in t index) |

Readout a value from a given location and return it as a float value |

write(int index, XF_TNAME(T,NP C) val) |

Writes a packed (for multi-pixel/clock) value into the given location. |

write_float(i nt index, float val) |

Writes a float value into the given location. |

type() |

Returns the type of the image. |

depth() |

Returns the depth of the image |

channels() |

Returns number of channels of the image |

~Mat() |

This is a default destructor of the Mat object. |

Template parameters of the xf::cv::Mat class are used to set the depth

of the pixel, number of channels in the image, number of pixels packed

per word, maximum number of rows and columns of the image. The following

table lists the template parameters and their descriptions:

Parameters |

Description |

|---|---|

TYPE |

Type of the pixel data. For example, XF_8UC1 stands for 8-bit unsigned and one channel pixel. More types can be found in include/common/xf_params.h. |

HEIGHT |

Maximum height of an image. |

WIDTH |

Maximum width of an image. |

NPC |

The number of pixels to be packed per word. For instance, XF_NPPC1 for 1 pixel per word; and XF_NPPC8 for 8 pixels per word. |

Pixel-Level Parallelism¶

The amount of parallelism to be implemented in a function from Vitis Vision is kept as a configurable parameter. In most functions, there are two options for processing data.

Single-pixel processing

Processing eight pixels in parallel

The following table describes the options available for specifying the level of parallelism required in a particular function:

Option |

Description |

|---|---|

XF_NPPC1 |

Process 1 pixel per clock cycle |

XF_NPPC2 |

Process 2 pixels per clock cycle |

XF_NPPC4 |

Process 4 pixels per clock cycle |

XF_NPPC8 |

Process 8 pixels per clock cycle |

Macros to Work With Parallelism¶

There are two macros that are defined to work with parallelism.

The

XF_NPIXPERCYCLE(flags)macro resolves to the number of pixels processed per cycle.XF_NPIXPERCYCLE(XF_NPPC1)resolves to 1XF_NPIXPERCYCLE(XF_NPPC2)resolves to 2XF_NPIXPERCYCLE(XF_NPPC4)resolves to 4XF_NPIXPERCYCLE(XF_NPPC8)resolves to 8

The

XF_BITSHIFT(flags)macro resolves to the number of times to shift the image size to right to arrive at the final data transfer size for parallel processing.XF_BITSHIFT(XF_NPPC1)resolves to 0XF_BITSHIFT(XF_NPPC2)resolves to 1XF_BITSHIFT(XF_NPPC4)resolves to 2XF_BITSHIFT(XF_NPPC8)resolves to 3

Data Types¶

Data types will differ, depending on the combination of the depth of pixels and the number of channels in the image. The generic nomenclature of the parameter is listed below.

XF_<Number of bits per pixel><signed (S) or unsigned (U) or float (F)>C<number of channels>

For example, for an 8-bit pixel - unsigned - 1 channel the data type is

XF_8UC1.

The following table lists the available data types for the xf::cv::Mat

class:

Option |

Number of bits per Pixel |

Unsigned/ Signed/ Float Type |

Number of Channels |

|---|---|---|---|

XF_8UC1 |

8 |

Unsigned |

1 |

XF_16UC1 |

16 |

Unsigned |

1 |

XF_16SC1 |

16 |

Signed |

1 |

XF_32UC1 |

32 |

Unsigned |

1 |

XF_32FC1 |

32 |

Float |

1 |

XF_32SC1 |

32 |

Signed |

1 |

XF_8UC2 |

8 |

Unsigned |

2 |

XF_8UC4 |

8 |

Unsigned |

4 |

XF_8UC3 |

8 |

Unsigned |

3 |

XF_2UC1 |

2 |

Unsigned |

1 |

Manipulating Data Type¶

Based on the number of pixels to process per clock cycle and the type

parameter, there are different possible data types. The Vitis Vision library

uses these datatypes for internal processing and inside the xf::cv::Mat

class. The following are a few supported types:

XF_TNAME(TYPE,NPPC)resolves to the data type of the data member of thexf::cv::Matobject. For instance,XF_TNAME(XF_8UC1,XF_NPPC8)resolves toap_uint<64>.Word width = pixel depth * number of channels * number of pixels to process per cycle (NPPC).XF_DTUNAME(TYPE,NPPC)resolves to the data type of the pixel. For instance,XF_DTUNAME(XF_32FC1,XF_NPPC1)resolves tofloat.XF_PTSNAME(TYPE,NPPC)resolves to the ‘C’ data type of the pixel. For instance,XF_PTSNAME (XF_16UC1,XF_NPPC2)resolves tounsigned short.

Note

ap_uint<>, ap_int<>, ap_fixed<>, and ap_ufixed<> types belong to the high-level synthesis (HLS) library. For more information, see the Vivado Design Suite User Guide: High-Level Synthesis (UG902).

xf::cv::imread¶

The function xf::cv::imread loads an image from the specified file path, copies into xf::cv::Mat and returns it. If the image cannot be read (because of missing file, improper permissions, unsupported or invalid format), the function exits with a non-zero return code and an error statement.

Note

In an HLS standalone mode like Cosim, use cv::imread followed by copyTo function, instead of xf::cv::imread.

API Syntax

template<int PTYPE, int ROWS, int COLS, int NPC>

xf::cv::Mat<PTYPE, ROWS, COLS, NPC> imread (char *filename, int type)

Parameter Descriptions

The table below describes the template and the function parameters.

Parameter |

Description |

|---|---|

PTYPE |

Input pixel type. Value should be in accordance with the ‘type’ argument’s value. |

ROWS |

Maximum height of the image to be read |

COLS |

Maximum width of the image to be read |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

filename |

Name of the file to be loaded |

type |

Flag that depicts the type of image. The values are:

|

xf::cv::imwrite¶

The function xf::cv::imwrite saves the image to the specified file from the given xf::cv::Mat. The image format is chosen based on the file name extension. This function internally uses cv::imwrite for the processing. Therefore, all the limitations of cv::imwrite are also applicable to xf::cv::imwrite.

API Syntax

template <int PTYPE, int ROWS, int COLS, int NPC>

void imwrite(const char *img_name, xf::cv::Mat<PTYPE, ROWS, COLS, NPC> &img)

Parameter Descriptions

The table below describes the template and the function parameters.

Parameter |

Description |

|---|---|

PTYPE |

Input pixel type. Supported types are: XF_8UC1, XF_16UC1, XF_8UC4, and XF_16UC4 |

ROWS |

Maximum height of the image to be read |

COLS |

Maximum width of the image to be read |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

img_name |

Name of the file with the extension |

img |

xf::cv::Mat array to be saved |

xf::cv::absDiff¶

The function xf::cv::absDiff computes the absolute difference between each individual pixels of an xf::cv::Mat and a cv::Mat, and returns the difference values in a cv::Mat.

API Syntax

template <int PTYPE, int ROWS, int COLS, int NPC>

void absDiff(cv::Mat &cv_img, xf::cv::Mat<PTYPE, ROWS, COLS, NPC>& xf_img, cv::Mat &diff_img )

Parameter Descriptions

The table below describes the template and the function parameters.

Parameter |

Description |

|---|---|

PTYPE |

Input pixel type |

ROWS |

Maximum height of the image to be read |

COLS |

Maximum width of the image to be read |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1, XF_NPPC4, and XF_NPPC8 for 1-pixel, 4-pixel, and 8-pixel parallel operations respectively. |

cv_img |

cv::Mat array to be compared |

xf_img |

xf::cv::Mat array to be compared |

diff_img |

Output difference image(cv::Mat) |

xf::cv::convertTo¶

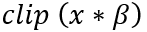

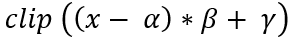

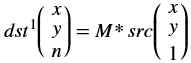

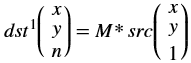

The xf::cv::convertTo function performs bit depth conversion on each individual pixel of the given input image. This method converts the source pixel values to the target data type with appropriate casting.

dst(x,y)= cast<target-data-type>(α(src(x,y)+β))

Note: The output and input Mat cannot be the same. That is, the converted image cannot be stored in the Mat of the input image.

API Syntax

template<int DST_T> void convertTo(xf::cv::Mat<DST_T,ROWS, COLS, NPC> &dst, int ctype, double alpha=1, double beta=0)

Parameter Descriptions

The table below describes the template and function parameters.

Parameter |

Description |

|---|---|

DST_T |

Output pixel type. Possible values are XF_8UC1, XF_16UC1, XF_16SC1, and XF_32SC1. |

ROWS |

Maximum height of image to be read |

COLS |

Maximum width of image to be read |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1, XF_NPPC4, and XF_NPPC8 for 1-pixel, 4-pixel, and 8-pixel parallel operations respectively. XF_32SC1 and XF_NPPC8 combination is not supported. |

dst |

Converted xf Mat |

ctype |

Conversion type : Possible values are listed here.

//Up-convert:

|

alpha |

Optional scale factor |

beta |

Optional delta added to the scaled values |

Vitis Vision Library Functions¶

The Vitis Vision library is a set of select OpenCV functions optimized for Zynq-7000 and Zynq UltraScale+ MPSoC devices. The maximum resolution supported for all the functions is 4K, except Houghlines and HOG (RB mode).

Note

Resolution Conversion (Resize) in 8 pixel per cycle mode, Dense Pyramidal LK Optical Flow, and Dense Non-Pyramidal LK Optical Flow functions are not

supported on the Zynq-7000 SoC ZC702 devices, due to the higher resource utilization.

Note

Number of pixel per clock depends on the maximum bus width a device can support. For example: Zynq-7000 SoC has 64-bit interface and so for a pixel type 16UC1, maximum of four pixel per clock (XF_NPPC4) is possible.

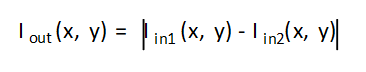

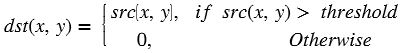

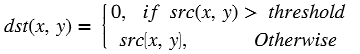

Absolute Difference¶

API Syntax

The absdiff function finds the pixel wise absolute difference

between two input images and returns an output image. The input and the

output images must be the XF_8UC1 type.

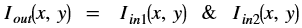

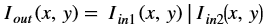

Where,

Iout(x, y) is the intensity of output image at (x,y) position.

Iin1(x, y) is the intensity of first input image at (x,y) position.

Iin2(x, y) is the intensity of second input image at (x,y) position.

template<int SRC_T, int ROWS, int COLS, int NPC=1>

void absdiff(

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input and Output pixel type. Only 8-bit, unsigned, 1 and 3 channels are supported (XF_8UC1 and XF_8UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be multiple of 8, for 8-pixel operation. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

62 |

67 |

17 |

8 Pixel |

150 |

0 |

0 |

67 |

234 |

39 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.69 |

Deviation from OpenCV

There is no deviation from OpenCV, except that the absdiff function

supports 8-bit pixels.

Accumulate¶

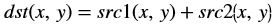

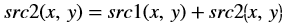

The accumulate function adds an image (src1) to the accumulator

image (src2), and generates the accumulated result image (dst).

API Syntax

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void accumulate (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int DST_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type. Only 8-bit, unsigned, 1 and 3 channels are supported (XF_8UC1 and XF_8UC3) |

DST_T |

Output pixel type. Only 16-bit, unsigned, 1 and 3 channels are supported (XF_16UC1 and XF_16UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Recommend using a multiple of 8, for an 8-pixel operation. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

62 |

55 |

12 |

8 Pixel |

150 |

0 |

0 |

389 |

285 |

61 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process 4K 3 Channel image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

207 |

72 |

32 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

Deviation from OpenCV

Whereas, in the Vitis Vision implementation, the accumulated image is stored separately, as shown below:

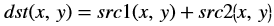

Accumulate Squared¶

The accumulateSquare function adds the square of an image (src1) to

the accumulator image (src2) and generates the accumulated result (dst).

The accumulated result is a separate argument in the function, instead of having src2 as the accumulated result. In this implementation, having a bi-directional accumulator is not possible as the function makes use of streams.

API Syntax

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void accumulateSquare (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int DST_T, int ROWS, int COLS, int NPC> dst)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type. Only 8-bit, unsigned, 1 and 3 channels are supported (XF_8UC1 and XF_8UC3) |

DST_T |

Output pixel type. Only 16-bit, unsigned, 1 and 3 channels are supported (XF_16UC1 and XF_16UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image (must be multiple of 8, for 8-pixel operation) |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

71 |

52 |

14 |

8 Pixel |

150 |

0 |

8 |

401 |

247 |

48 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process 4K 3 Channel image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

3 |

227 |

86 |

37 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.6 |

Deviation from OpenCV

In OpenCV the accumulated squared image is stored in the second input image. The src2 image acts as input as well as output.

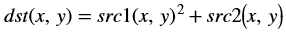

Accumulate Weighted¶

The accumulateWeighted function computes the weighted sum of the

input image (src1) and the accumulator image (src2) and generates the

result in dst.

The accumulated result is a separate argument in the function, instead of having src2 as the accumulated result. In this implementation, having a bi-directional accumulator is not possible, as the function uses streams.

API Syntax

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void accumulateWeighted (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int DST_T, int ROWS, int COLS, int NPC> dst,

float alpha )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type. Only 8-bit, unsigned, 1 and 3 channels are supported (XF_8UC1 and XF_8UC3) |

DST_T |

Output pixel type. Only 16-bit, unsigned, 1 and 3 channels are supported (XF_16UC1 and XF_16UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Recommend multiples of 8, for an 8-pixel operation. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

alpha |

Weight applied to input image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

5 |

295 |

255 |

52 |

8 Pixel |

150 |

0 |

19 |

556 |

476 |

88 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4K 3 Channel image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

9 |

457 |

387 |

95 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

Deviation from OpenCV

The resultant image in OpenCV is stored in the second input image. The src2 image acts as input as well as output, as shown below:

Whereas, in Vitis Vision implementation, the accumulated weighted image is stored separately.

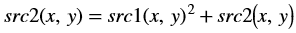

AddS¶

The AddS function performs the addition operation between pixels of input image src and given scalar value scl and stores the result in dst.

dst(x,y)= src(x,y) + scl

Where (x,y) is the spatial coordinate of the pixel.

API Syntax

template<int POLICY_TYPE, int SRC_T, int ROWS, int COLS, int NPC =1>

void addS(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src1, unsigned char _scl[XF_CHANNELS(SRC_T,NPC)],xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _dst)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type. 8-bit, unsigned, 1 channel is supported (XF_8UC1). |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. In case of N-pixel parallelism, width should be multiple of N. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

_src1 |

First input image |

_scl |

Input scalar value, the size should be number of channels. |

_dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization of the AddS function in both the resource optimized (8 pixel) mode and normal mode, as generated using Vivado HLS 2019.1 version tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA.

Name |

Resource Utilization |

|

|---|---|---|

1 pixel per clock operation |

8 pixel per clock operation |

|

300 MHz |

150 MHz |

|

BRAM_18K |

0 |

0 |

DSP48E |

0 |

0 |

FF |

100 |

101 |

LUT |

52 |

185 |

CLB |

20 |

45 |

Performance Estimate

The following table summarizes a performance estimate of the kernel in different configurations, generated using Vivado HLS 2019.1 tool for Xczu9eg-ffvb1156-1-i-es1 FPGA to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

Addweighted¶

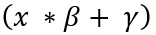

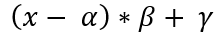

The addweighted function calculates a weighted sum of two input images src1, src2 and generates the result in dst.

dst(x,y)= src1(x,y)*alpha+src2(x,y)*beta+ gamma

API Syntax

template< int SRC_T , int DST_T, int ROWS, int COLS, int NPC=1>

void addWeighted(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src1, float alpha, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src2, float beta, float gamma, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _dst)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input Pixel Type. 8-bit, unsigned,1 channel is supported (XF_8UC1) |

DST_T |

Output Pixel Type. 8-bit, unsigned,1 channel is supported (XF_8UC1) |

ROWS |

Maximum height of input and output image |

COLS |

Maximum width of input and output image. In case of N-pixel parallelism, width should be multiple of N |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

_src1 |

First Input image |

Alpha |

Weight applied on first image |

_src2 |

Second Input image |

Beta |

Weight applied on second image |

gamma |

Scalar added to each sum |

_dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization of the Addweighted function in Resource optimized (8 pixel) mode and normal mode, as generated in Vivado HLS 2019.1 version tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA.

Name |

Resource Utilization |

|

|---|---|---|

1 pixel per clock operation |

8 pixel per clock operation |

|

300 MHz |

150 MHz |

|

BRAM_18K |

0 |

0 |

DSP48E |

11 |

25 |

FF |

903 |

680 |

LUT |

851 |

1077 |

CLB |

187 |

229 |

Performance Estimate

The following table summarizes a performance estimate of the kernel in different configurations, generated using Vivado HLS 2019.1 tool for Xczu9eg-ffvb1156-1-i-es1 FPGA to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

Autowhitebalance¶

Grayworld whitebalancing algorithm:

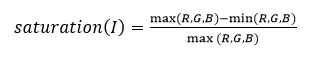

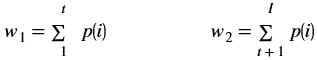

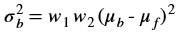

This algorithm scales the values of pixels based on a gray-world assumption which states that the average of all channels should result in a gray image. It adds a modification which thresholds pixels based on their saturation value and only uses pixels below the provided threshold in finding average pixel values. Saturation is calculated using the following for a 3-channel RGB image per pixel I and is in the range [0, 1]:

A threshold of 1 means that all pixels are used to white-balance, while a threshold of 0 means no pixels are used. Lower thresholds are useful in white-balancing saturated images.

Simple whitebalancing algorithm:

A simple white balance algorithm that works by independently stretching each of the input image channels to the specified range(maximum and minimum). Computes channel wise intensity histogram and ignores p% maximum and minimum values and finally normalize each channel with min and max. For increased robustness it ignores the top and bottom \(p\%\ \ (4\%\ is\ fixed)\) of pixel values.

API Syntax

template< int SRC_T,int DST_T, int ROWS, int COLS, int NPC = 1,bool WB_TYPE>void balanceWhite(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & src1,xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & src2, xf::cv::Mat<DST_T, ROWS, COLS, NPC> & dst,float thresh,float inputMin,float inputMax,float outputMin,float outputMax)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input Pixel Type. |

DST_T |

Output Pixel Type. |

ROWS |

Maximum height of input and output image (Must be multiple of NPC) |

COLS |

Maximum width of input and output image (Must be multiple of NPC) |

NPC |

Number of Pixels to be processed per cycle. |

WB_TYPE |

White balance type. Supported types are Gray world and simple. |

Src1 |

Input image. |

Src2 |

Input image. |

dst |

Output image. |

thresh |

Threshold value, which is used in gray world white balance method to compute average pixel values below the threshold value. |

inputMin |

Input image range minimum value. |

inputMax |

Input image range maximum value. |

outputMin |

Output image range minimum value. |

outputMax |

Output image range maximum value. |

Resource Utilization

The following table summarizes the resource utilization of the kernel in different configurations, generated using Vivado HLS 2019.2 tool for the Xilinx xc7vx485t-ffg1157-1 FPGA, to process a 4K image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 pixel |

300 |

14 |

10 |

4798 |

4953 |

1757 |

2 pixel |

300 |

14 |

10 |

8335 |

8535 |

2901 |

Performance Estimate

The following table summarizes a performance estimate of the kernel in different configurations, as generated using Vivado HLS 2019.2 tool for the Xilinx xc7vx485t-ffg1157-1 FPGA, to process a 4K image.

Operating Mode |

Operating Frequency (MHz) |

Latency Estimate |

|---|---|---|

Max (ms) |

||

1 pixel |

300 |

55.2 for still image(27.9 for video stream) |

2 pixel |

300 |

28 for still image(14.2 for video stream) |

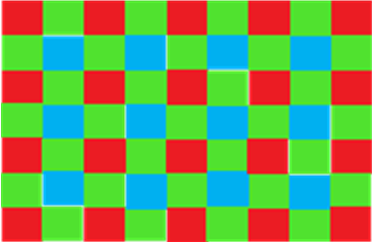

Badpixelcorrection¶

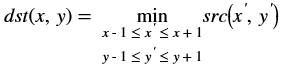

An image sensor may have a certain number of defective/bad pixels that may be the result of manufacturing faults or variations in pixel voltage levels based on temperature or exposure. The Badpixelcorrection module removes the defective pixels in the image using below operation.

If the middle pixel value is lesser than minimum neighborhood value, will consider minimum neighborhood value as mid pixel, otherwise mid pixel value is greater than maximum neighborhood value, will consider maximum neighborhood as mid pixel.

API Syntax

template<int TYPE, int ROWS, int COLS, int NPPC=1, int BORDER_T=XF_BORDER_CONSTANT, int USE_URAM=0>void badpixelcorrection(xf::cv::Mat<TYPE, ROWS, COLS, NPPC> &_src,xf::cv::Mat<TYPE, ROWS, COLS, NPPC> &_dst)

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

TYPE |

Input and Output Pixel Type. |

ROWS |

Maximum height of input and output image (Must be multiple of NPPC) |

COLS |

Maximum width of input and output image (Must be multiple of NPPC) |

NPPC |

Number of Pixels to be processed per cycle. |

BORDER_T |

Border Type supported is XF_BORDER_CONSTANT |

USE_URAM |

Enable to map storage structures to UltraRAM. |

_src |

Input Bayer image |

_dst |

Output Bayer image |

Resource Utilization

The following table summarizes the resource utilization of the kernel in different configurations, generated using Vivado HLS 2019.2 tool for the Xilinx xc7vx485t-ffg1157-1 FPGA, to process a 4K image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

SLICE |

||

1 pixel |

300 |

10 |

0 |

979 |

744 |

355 |

2 pixel |

300 |

10 |

0 |

1148 |

1177 |

458 |

Performance Estimate

The following table summarizes a performance estimate of the kernel in different configurations, as generated using Vivado HLS 2019.2 tool for the Xilinx xc7vx485t-ffg1157-1, to process 4K image.

Operating Mode |

Operating Frequency (MHz) |

Latency Estimate |

|---|---|---|

Max (ms) |

||

1 pixel |

300 |

27.8 |

2 pixel |

300 |

14.2 |

Bilateral Filter¶

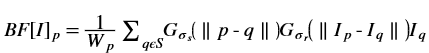

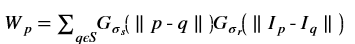

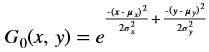

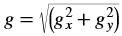

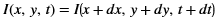

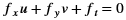

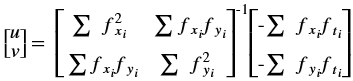

In general, any smoothing filter smoothens the image which will affect the edges of the image. To preserve the edges while smoothing, a bilateral filter can be used. In an analogous way as the Gaussian filter, the bilateral filter also considers the neighboring pixels with weights assigned to each of them. These weights have two components, the first of which is the same weighing used by the Gaussian filter. The second component takes into account the difference in the intensity between the neighboring pixels and the evaluated one.

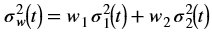

is a gaussian filter with variance

is a gaussian filter with variance  .

.The gaussian filter is given by:

API Syntax

template<int FILTER_SIZE, int BORDER_TYPE, int TYPE, int ROWS, int COLS, int NPC=1>

void bilateralFilter (

xf::cv::Mat<int TYPE, int ROWS, int COLS, int NPC> src,

xf::cv::Mat<int TYPE, int ROWS, int COLS, int NPC> dst,

float sigma_space, float sigma_color )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

FILTER_SIZE |

Filter size. Filter size of 3 (XF_FILTER_3X3), 5 (XF_FILTER_5X5) and 7 (XF_FILTER_7X7) are supported |

BORDER_TYPE |

Border type supported is XF_BORDER_CONSTANT |

TYPE |

Input and output pixel type. Only 8-bit, unsigned, 1 channel, and 3 channels are supported (XF_8UC1 and XF_8UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image (must be multiple of 8, for 8-pixel operation) |

NPC |

Number of pixels to be processed per cycle; this function supports XF_NPPC1 and XF_NPPC8. |

src |

Input image |

dst |

Output image |

sigma_space |

Standard deviation of filter in spatial domain |

sigma_color |

Standard deviation of filter used in color space |

Resource Utilization

The following table summarizes the resource utilization of the kernel in different configurations, generated using Vivado HLS 2019.1 version tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to progress a grayscale HD (1080x1920) image.

Operating Mode |

Filter Size |

Operating Frequency (MHz) |

Utilization Estimate |

|||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

|||

1 Pixel |

3x3 |

300 |

6 |

22 |

4934 |

4293 |

5x5 |

300 |

12 |

30 |

5481 |

4943 |

|

7x7 |

300 |

37 |

48 |

7084 |

6195 |

|

The following table summarizes the resource utilization of the kernel in different configurations, generated using Vivado HLS 2019.1 version tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to progress a 4K 3 channel image.

Operating Mode |

Filter Size |

Operating Frequency (MHz) |

Utilization Estimate |

|||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

|||

1 Pixel |

3x3 |

300 |

12 |

32 |

8342 |

7442 |

5x5 |

300 |

27 |

57 |

10663 |

8857 |

|

7x7 |

300 |

49 |

107 |

12870 |

12181 |

|

Performance Estimate

The following table summarizes a performance estimate of the kernel in different configurations, as generated using Vivado HLS 2019.1 tool for Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Filter Size |

Latency Estimate |

|---|---|---|

300 MHz |

||

Max Latency (ms) |

||

1 pixel |

3x3 |

7.18 |

5x5 |

7.20 |

|

7x7 |

7.22 |

Deviation from OpenCV

Unlike OpenCV, Vitis Vision only supports filter sizes of 3, 5 and 7.

Bit Depth Conversion¶

The convertTo function converts the input image bit depth to the

required bit depth in the output image.

API Syntax

template <int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void convertTo(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src_mat, xf::cv::Mat<DST_T, ROWS, COLS, NPC> &_dst_mat, ap_uint<4> _convert_type, int _shift)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type. 8-bit, unsigned, 1 channel (XF_8UC1), 16-bit, unsigned, 1 channel (XF_16UC1), 16-bit, signed, 1 channel (XF_16SC1), 32-bit, signed, 1 channel (XF_32SC1) are supported. |

DST_T |

Output pixel type. 8-bit, unsigned, 1 channel (XF_8UC1), 16-bit, unsigned, 1 channel (XF_16UC1), 16-bit, signed, 1 channel (XF_16SC1), 32-bit, signed, 1 channel (XF_32SC1) are supported. |

ROWS |

Height of input and output images |

COLS |

Width of input and output images |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. XF_NPPC8 is not supported with the 32-bit input and output pixel type. |

_src_mat |

Input image |

_dst_mat |

Output image |

_convert_ty pe |

This parameter specifies the type of conversion required. (See XF_convert_bit_depth_e enumerated type in file xf_params.h for possible values.) |

_shift |

Optional scale factor |

Possible Conversions

The following table summarizes supported conversions. The rows are possible input image bit depths and the columns are corresponding possible output image bit depths (U=unsigned, S=signed).

INPUT/OUTPUT |

U8 |

U16 |

S16 |

U32 |

S32 |

|---|---|---|---|---|---|

U8 |

NA |

yes |

yes |

NA |

yes |

U16 |

yes |

NA |

NA |

NA |

yes |

S16 |

yes |

NA |

NA |

NA |

yes |

U32 |

NA |

NA |

NA |

NA |

NA |

S32 |

yes |

yes |

yes |

NA |

NA |

Resource Utilization

The following table summarizes the resource utilization of the convertTo function, generated using Vivado HLS 2019.1 tool for the Xilinx® Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

8 |

581 |

523 |

119 |

8 Pixel |

150 |

0 |

8 |

963 |

1446 |

290 |

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

8 |

591 |

541 |

124 |

8 Pixel |

150 |

0 |

8 |

915 |

1500 |

308 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.69 |

Bitwise AND¶

The bitwise_and function performs the bitwise AND operation for each

pixel between two input images, and returns an output image.

Where,

is the intensity of output image at (x, y) position

is the intensity of output image at (x, y) position is the intensity of first input image at (x, y) position

is the intensity of first input image at (x, y) position is the intensity of second input image at (x, y) position

is the intensity of second input image at (x, y) position

API Syntax

template<int SRC_T, int ROWS, int COLS, int NPC=1>

void bitwise_and (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input and output pixel type. Supports 1 channel and 3 channels (XF_8UC1 and XF_8UC3) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image (must be a multiple of 8, for 8 pixel mode) |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations, respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

62 |

44 |

10 |

8 Pixel |

150 |

0 |

0 |

59 |

72 |

13 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4K 3Channel image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

155 |

61 |

22 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

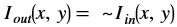

Bitwise NOT¶

The bitwise_not function performs the pixel wise bitwise NOT

operation for the pixels in the input image, and returns an output

image.

Where,

is the intensity of output image at (x, y) position

is the intensity of output image at (x, y) position is the intensity of input image at (x, y) position

is the intensity of input image at (x, y) position

API Syntax

template<int SRC_T, int ROWS, int COLS, int NPC=1>

void bitwise_not (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input and output pixel type. Supports 1 channel and 3 channels (XF_8UC1 and XF_8UC3). |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be a multiple of 8 for 8 pixel mode. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations, respectively. |

src |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Table 46. bitwise_not Function Resource Utilization Summary

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

97 |

78 |

20 |

8 Pixel |

150 |

0 |

0 |

88 |

97 |

21 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4K 3Channel image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

155 |

61 |

22 |

… rubric:: Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

Bitwise OR¶

The

bitwise_orfunction performs the pixel wise bitwise OR

operation between two input images, and returns an output image.

Where,

is the intensity of output image at (x, y) position

is the intensity of output image at (x, y) position is the intensity of first input image at (x, y) position

is the intensity of first input image at (x, y) position is the intensity of second input image at (x, y) position

is the intensity of second input image at (x, y) position

API Syntax

template<int SRC_T, int ROWS, int COLS, int NPC=1>

void bitwise_or (

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input and output pixel type. Supports 1 channel and 3 channels (XF_8UC1 and XF_8UC3). |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be multiple of 8, for 8 pixel mode. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

62 |

44 |

10 |

8 Pixel |

150 |

0 |

0 |

59 |

72 |

13 |

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4K 3Channel image

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

155 |

61 |

22 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

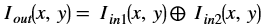

Bitwise XOR¶

The bitwise_xor function performs the pixel wise bitwise XOR

operation between two input images, and returns an output image, as

shown below:

Where,

is the intensity of output image at (x, y) position

is the intensity of output image at (x, y) position is the intensity of first input image at (x, y) position

is the intensity of first input image at (x, y) position is the intensity of second input image at (x, y) position

is the intensity of second input image at (x, y) position

API Syntax

template<int SRC_T, int ROWS, int COLS, int NPC=1>

void bitwise_xor(

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src1,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> src2,

xf::cv::Mat<int SRC_T, int ROWS, int COLS, int NPC> dst )

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input and output pixel type. Supports 1 channel and 3 channels (XF_8UC1 and XF_8UC3). |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be multiple of 8, for 8 pixel mode. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

src1 |

Input image |

src2 |

Input image |

dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image:

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

0 |

62 |

44 |

10 |

8 Pixel |

150 |

0 |

0 |

59 |

72 |

13 |

Performance Estimate

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4k Channel image

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

1 |

155 |

61 |

22 |

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image:

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.9 |

8 pixel operation (150 MHz) |

1.7 |

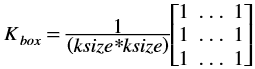

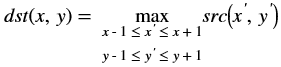

Box Filter¶

The boxFilter function performs box filtering on the input image. Box filter acts as a low-pass filter and performs blurring over the image. The boxFilter function or the box blur is a spatial domain linear filter in which each pixel in the resulting image has a value equal to the average value of the neighboring pixels in the image.

API Syntax

template<int BORDER_TYPE,int FILTER_TYPE, int SRC_T, int ROWS, int COLS,int NPC=1,bool USE_URAM=false>

void boxFilter(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src_mat,xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _dst_mat)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

FILTER_SIZE |

Filter size. Filter size of 3(XF_FILTER_3X3), 5(XF_FILTER_5X5) and 7(XF_FILTER_7X7) are supported |

BORDER_TYPE |

Border Type supported is XF_BORDER_CONSTANT |

SRC_T |

Input and output pixel type. 8-bit, unsigned, 16-bit unsigned and 16-bit signed, 1 channel is supported (XF_8UC1) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image (must be multiple of 8, for 8-pixel operation) |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. |

USE_URAM |

Enable to map storage structures to UltraRAM |

_src_mat |

Input image |

_dst_mat |

Output image |

Resource Utilization

The following table summarizes the resource utilization of the kernel in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a grayscale HD (1080x1920) image.

Operating Mode |

Filter Size |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

|||

1 Pixel |

3x3 |

300 |

3 |

1 |

545 |

519 |

104 |

5x5 |

300 |

5 |

1 |

876 |

870 |

189 |

|

7x7 |

300 |

7 |

1 |

1539 |

1506 |

300 |

|

8 Pixel |

3x3 |

150 |

6 |

8 |

1002 |

1368 |

264 |

5x5 |

150 |

10 |

8 |

1576 |

3183 |

611 |

|

7x7 |

150 |

14 |

8 |

2414 |

5018 |

942 |

|

The following table summarizes the resource utilization of the kernel in different configurations, generated using the Vivado HLS™ 2019.1 tool for the xczu7ev-ffvc1156-2-e FPGA, to process a grayscale 4K (3840x2160) image with UltraRAM enable.

Operating Mode |

Filter Size |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|---|

BRAM_18K |

URAM |

DSP_48Es |

FF |

LUT |

|||

1 Pixel |

3x3 |

300 |

0 |

1 |

1 |

821 |

521 |

5x5 |

300 |

0 |

1 |

1 |

1204 |

855 |

|

7x7 |

300 |

0 |

1 |

1 |

2083 |

1431 |

|

8 Pixel |

3x3 |

150 |

0 |

3 |

8 |

1263 |

1480 |

5x5 |

150 |

0 |

5 |

8 |

1771 |

3154 |

|

7x7 |

150 |

0 |

7 |

8 |

2700 |

5411 |

|

Performance Estimate

The following table summarizes the performance of the kernel in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image.

Operating Mode |

|

Filter Size |

Latency Estimate |

|---|---|---|---|

Max Latency (ms) |

|||

1 pixel |

300 |

3x3 |

7.2 |

300 |

5x5 |

7.21 |

|

300 |

7x7 |

7.22 |

|

8 pixel |

150 |

3x3 |

1.7 |

150 |

5x5 |

1.7 |

|

150 |

7x7 |

1.7 |

BoundingBox¶

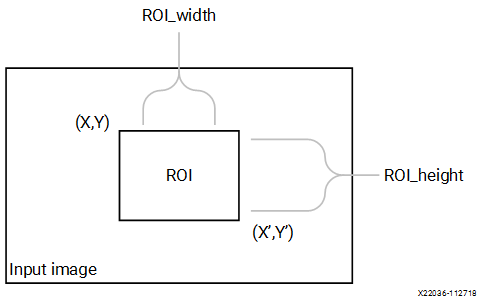

The boundingbox function highlights the region of interest (ROI)

from the input image using below equations.

P(X,Y) ≤ P(xi, yi) ≤ P(X,Y’)

P(X’,Y) ≤ P(xi, yi) ≤ P(X’,Y’)

Where,

P(xi, yi) - Current pixel location

P(X,Y) - Top left corner of ROI

P(X,Y’) - Top right corner of ROI

P(X’,Y) - Bottom left corner of ROI

P(X’,Y’) - Bottom Right of ROI

API Syntax

template<int SRC_T, int ROWS, int COLS, int MAX_BOXES=1, int NPC=1>

void boundingbox(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src_mat, xf::cv::Rect_<int> *roi , xf::cv::Scalar<4,unsigned char > *color, int num_box)

Parameter Descriptions

The following table describes the template and the function parameters.

Parameter |

Description |

|---|---|

SRC_T |

Input pixel Type. Only 8-bit, unsigned, 1 channel and 3 channel is supported (XF_8UC1,XF_8UC3). |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be multiple of NPC. |

MAX_BOXES |

Maximum number of boxes, fixed to 5. |

NPC |

Number of pixels to be processed per cycle, possible options are XF_NPPC1 only. |

_src_mat |

Input image |

roi |

ROI is a |

color |

The |

num_box |

Number of boxes to be detected. It should be equal or less than MAX_BOXES. |

Resource Utilization

The following table summarizes the resource utilization in different configurations, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

5 |

4 |

2521 |

1649 |

409 |

Performance Estimate

The following table summarizes the performance of the kernel in 1-pixel mode as generated using Vivado HLS 2019.1 tool for the Xilinx xczu9eg-ffvb1156-2-i-es2 FPGA to process a grayscale 4K (2160x3840) image for highlighting 3 different boundaries (480x640, 100x200, 300x300).

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

0.15 |

Vitis Vision Reference

The xf::cv::boundingbox is complaint with below Vitis Vision function:

void rectangle(Mat& img, Rect rec, const Scalar& color, int thickness=1, int lineType=8, int shift=0 )

Canny Edge Detection¶

The Canny edge detector finds the edges in an image or video frame. It is one of the most popular algorithms for edge detection. Canny algorithm aims to satisfy three main criteria:

Low error rate: A good detection of only existent edges.

Good localization: The distance between edge pixels detected and real edge pixels have to be minimized.

Minimal response: Only one detector response per edge.

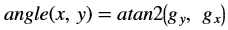

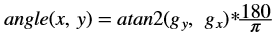

In this algorithm, the noise in the image is reduced first by applying a Gaussian mask. The Gaussian mask used here is the average mask of size 3x3. Thereafter, gradients along x and y directions are computed using the Sobel gradient function. The gradients are used to compute the magnitude and phase of the pixels. The phase is quantized and the pixels are binned accordingly. Non-maximal suppression is applied on the pixels to remove the weaker edges.

Edge tracing is applied on the remaining pixels to draw the edges on the image. In this algorithm, the canny up to non-maximal suppression is in one kernel and the edge linking module is in another kernel. After non-maxima suppression, the output is represented as 2-bit per pixel, Where:

00- represents the background01- represents the weaker edge11- represents the strong edge

The output is packed as 8-bit (four 2-bit pixels) in 1 pixel per cycle operation and packed as 16-bit (eight 2-bit pixels) in 8 pixel per cycle operation. For the edge linking module, the input is 64-bit, such 32 pixels of 2-bit are packed into a 64-bit. The edge tracing is applied on the pixels and returns the edges in the image.

API Syntax

The .. rubric:: API Syntax for Canny is:

template<int FILTER_TYPE,int NORM_TYPE,int SRC_T,int DST_T, int ROWS, int COLS,int NPC,int NPC1,bool USE_URAM=false>

void Canny(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src_mat,xf::cv::Mat<DST_T, ROWS, COLS, NPC1> & _dst_mat,unsigned char _lowthreshold,unsigned char _highthreshold)

The .. rubric:: API Syntax for EdgeTracing is:

template<int SRC_T, int DST_T, int ROWS, int COLS,int NPC_SRC,int NPC_DST,bool USE_URAM=false>

voidEdgeTracing(xf::cv::Mat<SRC_T, ROWS, COLS, NPC_SRC> & _src,xf::cv::Mat<DST_T, ROWS, COLS, NPC_DST> & _dst)

Parameter Descriptions

The following table describes the xf::cv::Canny template and function

parameters:

Parameter |

Description |

|---|---|

FILTER_TYPE |

The filter window dimensions. The options are 3 and 5. |

NORM_TYPE |

The type of norm used. The options for norm type are L1NORM and L2NORM. |

SRC_T |

Input pixel type. Only 8-bit, unsigned, 1 channel is supported (XF_8UC1) |

DST_T |

Output pixel type. Only XF_2UC1 is supported. The output in case of NPC=XF_NPPC1 is 8-bit and packing four 2-bit pixel values into 8-bit. The output in case of NPC=XF_NPPC8 is 16-bit, 8-bit, 2-bit pixel values are packing into 16-bit. |

ROWS |

Maximum height of input and output image |

COLS |

Maximum width of input and output image (must be a multiple of 8, in case of 8 pixel mode) |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 and XF_NPPC8 for 1 pixel and 8 pixel operations respectively. In XF_NPPC, the output image pixels are packed and precision is XF_NPPC4. In XF_NPPC8, output pixels precision is XF_NPPC8. |

USE_URAM |

Enable to map some storage structures to URAM |

_src_mat |

Input image |

_dst_mat |

Output image |

_lowthreshold |

The lower value of threshold for binary thresholding. |

_highthreshold |

The higher value of threshold for binary thresholding. |

The following table describes the EdgeTracing template and function

parameters:

Parameter |

Description |

|---|---|

SRC_T |

Input pixel type |

DST_T |

Output pixel type |

ROWS |

Maximum height of input and output image |

COLS |

Maximum width of input and output image (must be a multiple of 32) |

NPC_SRC |

Number of pixels to be processed per cycle. Fixed to XF_NPPC32. |

NPC_DST |

Number of pixels to be written to destination. Fixed to XF_NPPC8. |

USE_URAM |

Enable to map storage structures to URAM. |

_src |

Input image |

_dst |

Output image |

Resource Utilization

The following table summarizes the resource utilization of xf::cv::Canny

and EdgeTracing in different configurations, generated using Vivado

HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a

grayscale HD (1080x1920) image for Filter size is 3.

Name |

Resource Utilization |

|||||

|---|---|---|---|---|---|---|

1 pixel |

1 pixel |

8 pixel |

8 pixel |

Edge Linking |

Edge Linking |

|

L1NORM,FS:3 |

L2NORM,FS:3 |

L1NORM,FS:3 |

L2NORM,FS:3 |

|||

300 MHz |

300 MHz |

150 MHz |

150 MHz |

300 MHz |

150 MHz |

|

BRAM_18K |

22 |

18 |

36 |

32 |

84 |

84 |

DSP48E |

2 |

4 |

16 |

32 |

3 |

3 |

FF |

3027 |

3507 |

4899 |

6208 |

17600 |

14356 |

LUT |

2626 |

3170 |

6518 |

9560 |

15764 |

14274 |

CLB |

606 |

708 |

1264 |

1871 |

2955 |

3241 |

The following table summarizes the resource utilization of xf::cv::Canny

and EdgeTracing in different configurations, generated using Vivado HLS

2019.1 tool for the xczu7ev-ffvc1156-2-e FPGA, to process a grayscale 4K

image for Filter size is 3.

Name |

Resource Utilization |

|||||

|---|---|---|---|---|---|---|

1 pixel |

1 pixel |

8 pixel |

8 pixel |

Edge Linking |

Edge Linking |

|

L1NORM,FS:3 |

L2NORM,FS:3 |

L1NORM,FS:3 |

L2NORM,FS:3 |

|||

300 MHz |

300 MHz |

150 MHz |

150 MHz |

300 MHz |

150 MHz |

|

BRAM_18K |

10 |

8 |

3 |

3 |

4 |

4 |

URAM |

1 |

1 |

15 |

13 |

8 |

8 |

DSP48E |

2 |

4 |

16 |

32 |

8 |

8 |

FF |

3184 |

3749 |

5006 |

7174 |

5581 |

7054 |

LUT |

2511 |

2950 |

6695 |

9906 |

4092 |

6380 |

Performance Estimate

The following table summarizes the performance of the kernel in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a grayscale HD (1080x1920) image for L1NORM, filter size is 3 and including the edge linking module.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

10.8 |

8 pixel operation (150 MHz) |

8.5 |

Deviation from OpenCV

In OpenCV Canny function, the Gaussian blur is not applied as a pre-processing step.

Channel Combine¶

The merge function, merges single channel images into a

multi-channel image. The number of channels to be merged should be two, three or four.

API Syntax

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void merge(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src1, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src2, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src3, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src4, xf::cv::Mat<DST_T, ROWS, COLS, NPC> &_dst)

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void merge(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src1, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src2, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src3, xf::cv::Mat<DST_T, ROWS, COLS, NPC> &_dst)

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void merge(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src1, xf::cv::Mat<SRC_T, ROWS, COLS, NPC> &_src2, xf::cv::Mat<DST_T, ROWS, COLS, NPC> &_dst)

Parameter Descriptions

The following table describes the template and the function parameters.

Paramete r |

Description |

|---|---|

SRC_T |

Input pixel type. Only 8-bit, unsigned, 1, channel is supported (XF_8UC1) |

DST_T |

Output pixel type. 8-bit, unsigned,2,3 and 4 channels are supported (XF_8UC2, XF_8UC3 and XF_8UC4) |

ROWS |

Maximum height of input and output image. |

COLS |

Maximum width of input and output image. Must be multiple of 8 for 8 pixel mode. |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 for 1 pixel operation. |

_src1 |

Input single-channel image |

_src2 |

Input single-channel image |

_src3 |

Input single-channel image (only for 3 and 4 input config) |

_src4 |

Input single-channel image (only for 4 input config) |

_dst |

Output multi-channel image |

Resource Utilization

The following table summarizes the resource utilization of the merge function, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process 4 single-channel HD (1080x1920) images.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

8 |

494 |

386 |

85 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process 4 single channel HD (1080x1920) images.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.92 |

Channel Extract¶

The extractChannel function splits a multi-channel array (32-bit

pixel-interleaved data) into several single-channel arrays and returns a

single channel. The channel to be extracted is specified by using the

channel argument.

The value of the channel argument is specified by macros defined in the

xf_channel_extract_e enumerated data type. The following table

summarizes the possible values for the xf_channel_extract_e

enumerated data type:

Channel |

Enumerated Type |

|---|---|

Unknown |

XF_EXTRACT_CH_0 |

Unknown |

XF_EXTRACT_CH_1 |

Unknown |

XF_EXTRACT_CH_2 |

Unknown |

XF_EXTRACT_CH_3 |

RED |

XF_EXTRACT_CH_R |

GREEN |

XF_EXTRACT_CH_G |

BLUE |

XF_EXTRACT_CH_B |

ALPHA |

XF_EXTRACT_CH_A |

LUMA |

XF_EXTRACT_CH_Y |

Cb/U |

XF_EXTRACT_CH_U |

Cr/V/Value |

XF_EXTRACT_CH_V |

API Syntax

template<int SRC_T, int DST_T, int ROWS, int COLS, int NPC=1>

void extractChannel(xf::cv::Mat<SRC_T, ROWS, COLS, NPC> & _src_mat, xf::cv::Mat<DST_T, ROWS, COLS, NPC> & _dst_mat, uint16_t _channel)

Parameter Descriptions

The following table describes the template and the function parameters.

Paramete r |

Description |

|---|---|

SRC_T |

Input pixel type. Only 8-bit, unsigned, 4channel is supported (XF_8UC4) |

DST_T |

Output pixel type. Only 8-bit, unsigned, 1 channel is supported (XF_8UC1) |

ROWS |

Maximum height of input and output image |

COLS |

Maximum width of input and output image. Must be multiple of 8 for 8 pixel mode |

NPC |

Number of pixels to be processed per cycle; possible options are XF_NPPC1 for 1 pixel operation. |

_src_ma t |

Input multi-channel image |

_dst_ma t |

Output single channel image |

_channe l |

Channel to be extracted (See xf_channel_extract_e enumerated type in file xf_params.h for possible values.) |

Resource Utilization

The following table summarizes the resource utilization of the extractChannel function, generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1 FPGA, to process a 4 channel HD (1080x1920) image.

Operating Mode |

Operating Frequency (MHz) |

Utilization Estimate |

||||

|---|---|---|---|---|---|---|

BRAM_18K |

DSP_48Es |

FF |

LUT |

CLB |

||

1 Pixel |

300 |

0 |

8 |

508 |

354 |

96 |

Performance Estimate

The following table summarizes the performance in different configurations, as generated using Vivado HLS 2019.1 tool for the Xczu9eg-ffvb1156-1-i-es1, to process a 4 channel HD (1080x1920) image.

Operating Mode |

Latency Estimate |

|---|---|

Max Latency (ms) |

|

1 pixel operation (300 MHz) |

6.92 |

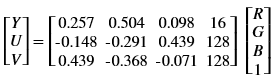

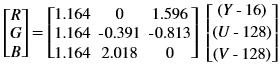

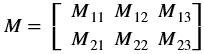

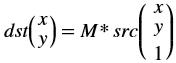

Color Conversion¶

The color conversion functions convert one image format to another image format, for the combinations listed in the following table. The rows represent the input formats and the columns represent the output formats. Supported conversions are discussed in the following sections.

I/O Formats |

RGBA |

NV12 |

NV21 |

IYUV |

UYVY |

YUYV |

YUV4 |

RGB |

BGR |

|---|---|---|---|---|---|---|---|---|---|

RGBA |

N/A |

For details, see the RGBA to NV12 |

For details, see the RGBA to NV21 |

For details, see the RGBA/RGB to IYUV |

For details, see the RGBA/RGB to YUV4 |

||||

NV12 |

For details, see the NV12 to RGBA |

N/A |

For details, see the NV12 to NV21/NV21 to NV12 |

For details, see the NV12 to IYUV |

For details, see the NV12/NV21 to UYVY/YUYV |

For details, see the NV12/NV21 to UYVY/YUYV |

For details, see the NV12 to YUV4 |

For details, see the NV12/NV21 to RGB/ BGR |

For details, see the NV12/NV21 to RGB/ BGR |

NV21 |