Hardware Architecture of the Platform¶

Introduction¶

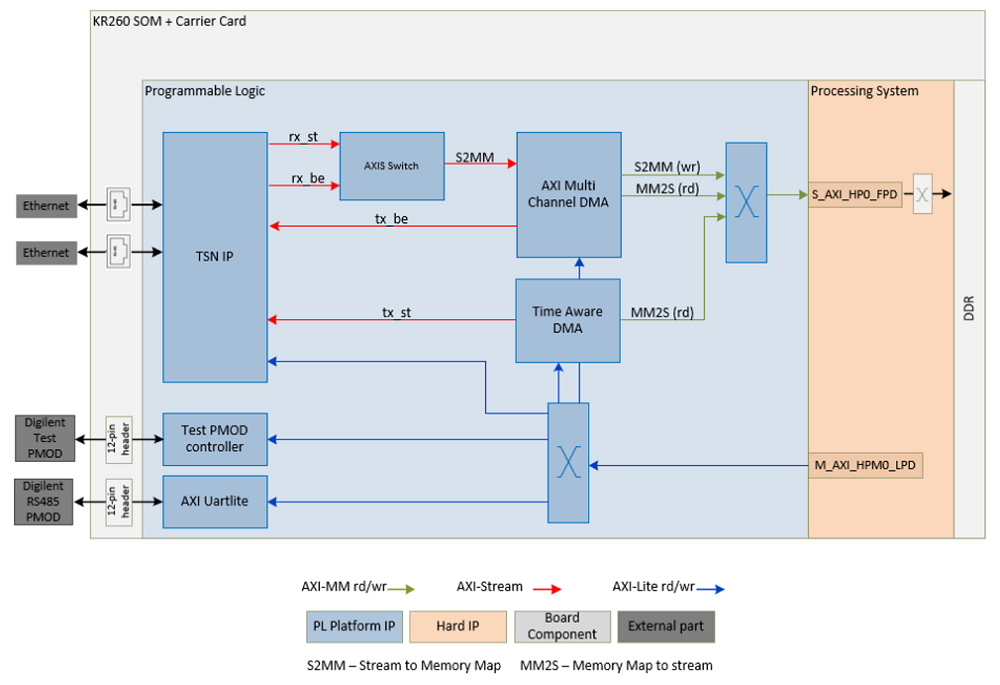

This section describes the design implemented in the Programmable Logic (PL).

The PL design provides a platform to support transmission of Ethernet traffic based on traffic shaping protocols. The traffic can be control information to be passed between different nodes in a Robotics system or between various Industrial Field devices. The requirement in these systems would be that the traffic is deterministic.

It also has an RS485 PMOD interface, which can be used to connect to RS485 peripherals such as actuators, sensors, and so on. These could be components in a Robotics system or part of a Field device.

The following figure shows the top-level hardware architecture of the reference design.

TSN IP¶

The main block in the PL design is the AMD LogiCORE™100M/1G TSN Subsystem IP, which implements IEEE 802.1 Time Sensitive Networking (TSN) Standards and provides a low latency Bridged Endpoint. The bridged endpoint solution consists of a 3-port switch, two ports connects to the network and one port connects to an internal Endpoint. In this design, RGMII interfaces connect to a Marvel physical-side interface (PHY) supporting a maximum bandwidth of 1 Gbps. The TSN IP is configured to support:

Network Time Synchronization- 1588 Precision Time Protocol (PTP)

Scheduled and Best Effort traffic types.

Time aware scheduling (IEEE 802.1 Qbv)

Frame replication and elimination (IEEE 802.1 CB)

Per Stream Filtering and Policing (IEEE 802.1 Qci)

For more information on the IP, refer to PG275.

Note: You will need access to 1GTSN Documentation Lounge to view the above document.

Time Aware DMA (TADMA)¶

TADMA is aware of the QBV schedule cycles and stream time slots. By using PTP generated time, it is capable of fetching frames for different streams/traffic classes from system memory (DDR) at precisely required time, providing excellent time precision for TSN traffic. In this design, TADMA fetches scheduled traffic from memory, based on the Qbv programming and passed it to the TSN IP for transmission.

For more information on the IP, refer to PG316.

Note: You will need access to 1GTSN Documentation Lounge to view the above document.

AXI Multichannel DMA (MCDMA)¶

The AXI MCDMA provides high-bandwidth direct memory access between memory (AXI Memory Mapped) and stream (AXI Stream) target peripherals. It supports both Memory Mapped to Stream (MM2S) and Stream to Memory Mapped (S2MM) transfers. The AXI MCDMA core provides Scatter Gather (SG) interface with multiple channel support with independent configuration. In this design, the MCDMA is responsible to fetch the Best Effort traffic for transmission by TSN IP. It reads frames from the DDR memory and passes data to the TSN IP on the AXI Stream interface. It is also responsible for writing the Schedule traffic and Best Effort traffic frames received from the TSN IP to the memory. The IP uses the S_AXI_HP0_FPD on the AMD Zynq™ UltraScale+™ MPSoC Processing System (PS) IP to read/write from/to the DDR memory.

For more information on the IP, refer to PG288.

AXI Stream Switch¶

The AXI4-Stream Switch provides configurable routing between masters and slaves. In this design, it is configured with two slaves and one master. The switch arbitrates when an end of a frame (tlast) is received, either on the received scheduled traffic (rx_st) stream or received best effort traffic (rx_be) stream.

For more information on the IP, refer to PG085.

Test PMOD controller¶

The Test PMOD controller is a user IP that drives the Digilent Test PMOD pins. The IP implements registers are detailed below.

| Register offset | Register name | Description |

|---|---|---|

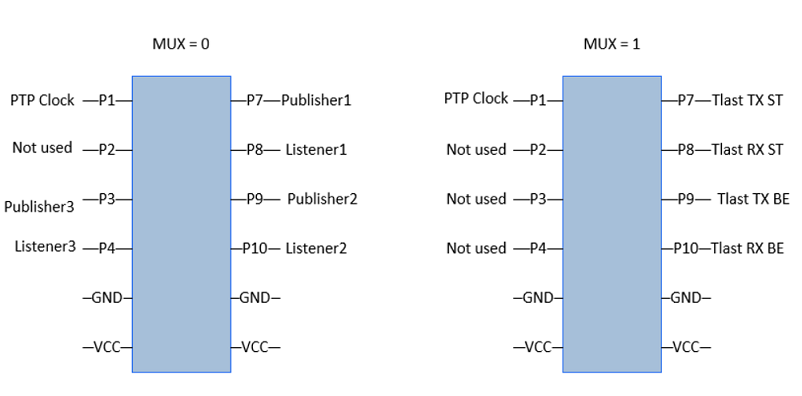

| 0x00 | slv_reg0 | Bit0 is a MUX enable. If 1 then drive Qbv signals on PMOD. If 0 drive TSN publisher/subscriber 8-bit signatures |

| 0x04 | slv_reg1 | 8-bit signature when publisher 1 transmits a TSN frame |

| 0x08 | slv_reg2 | 8-bit signature when subscriber 1 receives a TSN frame |

| 0x0c | slv_reg3 | 8-bit signature when publisher 2 transmits a TSN frame |

| 0x10 | slv_reg4 | 8-bit signature when subscriber 2 receives a TSN frame |

| 0x14 | slv_reg5 | 8-bit signature when publisher 3 transmits a TSN frame |

| 0x18 | slv_reg6 | 8-bit signature when subscriber 3 receives a TSN frame |

The TSN application can support multiple publishers and subscribers. When the publisher queues up a packet for transmission, it writes a unique 8-bit word to slv_reg*, which is then transmitted on the PMOD pins. Similarly, when the subscriber receives a packet, it writes a unique 8-bit word to slv_reg*, which is then transmitted on the PMOD pins. The PMOD pins of the publisher and the subscriber are hooked up to a scope and are used to measure an end-to-end application latency. The TSN pub sub application sets the MUX (slv_reg0) to 0 before writing the signature value. The figure below shows the mapping on the PMOD pins when MUX is set to 0 and 1.

To view scheduled and best effort traffic, the MUX value is set to 1. If Qbv schedule is set, for example, a time slot is programmed with 70% scheduled traffic and 30% best effort traffic, then viewing tlast signal of received scheduled traffic and tlast signal of received best effort traffic on a scope confirms that Qbv is working as expected. Tlast indicates the end of a packet. Transmit signals can also be monitored, but note these signals are on the outside of the TSN IP and the traffic is yet to be scheduled.

The other signal that is monitored to see if the Transmitter and Receiver clocks are in sync is the PTP clock.

For more information on how to use PMOD signals to check clock synchronization, to measure latency and confirm Qbv programming, refer to the application deployment page.

AXI Uartlite¶

The LogiCORE IP AXI UART Lite core converts AXI4 Lite register transactions to RS232 signaling. To support RS485, signaling a patch needs to be applied to the IP core. The AXI Uartlite IP patch is located at the following location and adds a Drive Enable signal to the IP.

$working_dir/platforms/vivado/kr260_tsn_rs485pmod/ip, or here, and the patch is also available at the support website here.

The Makefile copies the AXI Uartlite IP from the AMD Vivado™ install area and applies the patch.

To test an RS485 interface, the signals are connected to a Digilent PMOD R485 and a temperature sensor. The application running on the PS reads and writes to the AXI Uartlite registers and communicates with the temperature sensor using the MODBUS protocol.

For information on how to test the RS485 PMOD interface, refer to the application deployment page.

For an overview on RS485 and MODBUS, refer to this article.

Clocks, Resets and Interrupts¶

Clocks¶

The following table identifies the main clocks of the PL design, their source, clock frequency, and function.

| Clock | Clock Source | Clock Frequency | Funtion |

|---|---|---|---|

| CLK_IN_gem | External | 25 MHz | Clock source for clocking wizard (clk_wiz_0) generating clocks |

| clk_out1* | Clocking wizard | 200 MHz | TSN IP fifo clock, TADMA IP and MCDMA IP data transactions clock |

| clk_out2* | Clocking wizard | 125 MHz | TSN IP and TADMA IP Real Time clock (RTC) for internal timers for time sensitivity |

| clk_out3* | Clocking wizard | 300 MHz | reference clock for IDELAY control block for PHY operation on TSN IP |

| clk_out4* | Clocking wizard | 100 MHz | AXI-Lite clock to configure TSN IP, MCDMA IP, AXI Uartlite IP, Register interface IP |

*Clocks exposed as a Platform interface and can be used by an accelerator.

Resets¶

The following table summarizes the resets used in this design.

| Reset Source | Function |

|---|---|

| pl_resetn0 | PL reset for proc_sys_reset modules |

| rst_clk_wiz_0_100M | Synchronous resets for clk_out100M clock domain |

| rst_clk_wiz_0_125M | Synchronous resets for clk_out125M clock domain |

| rst_clk_wiz_0_200M | Synchronous resets for clk_out200M clock domain |

| rst_clk_wiz_0_300M | Synchronous resets for clk_out300M clock domain |

| proc_sys_reset_0 | Synchronous resets for ptp timer clock domain |

Interrupts¶

The following table lists the PL-to-PS interrupts used in this design. The AXI Interrupt controller IP connects the PL interrupts to the pl_ps_irq0 signal on the PS.

| Inerrupt ID | Instance |

|---|---|

| intr[0-7] | TSN IP |

| intr[8] | TADMA IP |

| intr[9-14] | MCDMA IP |

| intr[15] | AXI Uartlite IP |

| pl_ps_irq1 | Exposed as a Platform interface and can be used by an accelerator |

Resource Utilization¶

The resource utilization numbers on this platform post implementation is reported in the following table.

| Resource | Utilization | Available | Utilization % |

|---|---|---|---|

| LUT | 47061 | 117120 | 40.18 |

| LUTRAM | 3769 | 57600 | 6.54 |

| FF | 70328 | 234240 | 30.02 |

| BRAM | 79.5 | 144 | 55.21 |

| URAM | 13 | 64 | 20.31 |

| DSP | 35 | 1248 | 2.80 |

| IO | 43 | 186 | 22.75 |

| BUFG | 17 | 352 | 4.83 |

| MMCM | 1 | 4 | 25.0 |

Next Steps¶

Go back to the KR260 SOM ROS 2 Multi-Node Communications via TSN start page

Copyright© 2023 Advanced Micro Devices, Inc.