2. Introduction¶

The platform is designed to support a Versal VMK180 board for showcasing the MRMAC IP as a peripheral. It consists of MRMAC (x4) at 10G with each lane interfaced to one TX and RX channel of an independent MCDMA. The ACAP hardware that is supported on the Versal platform has the following features: It contains the Quad base GT in Programmable Logic (PL) to accommodate the movement of Ethernet packets. The output of the GTY is connected to the external NIC. The ethernet data packets are transferred using MRMAC via GT interface.

2.1. Platform¶

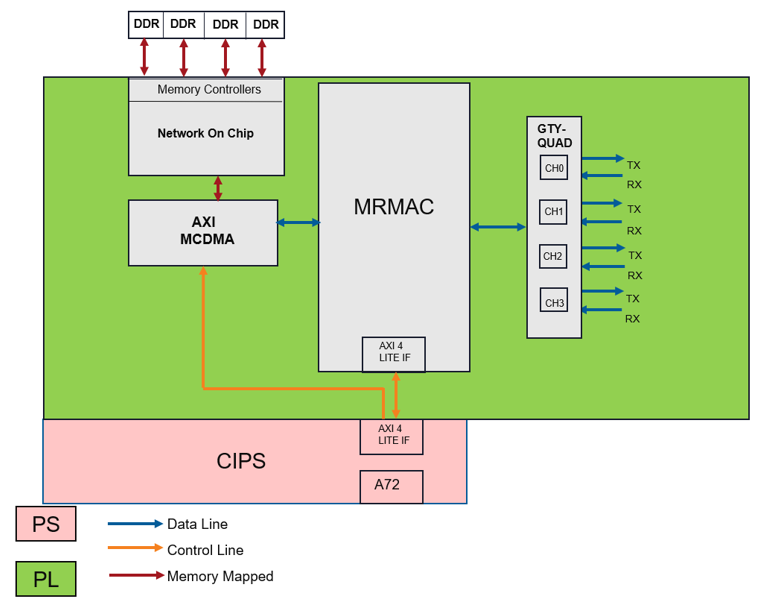

The following section provides the details of various components in the platform as illustrated in the figure:

- Control Interface and Processor Subsystem (CIPS):

The CIPS present in Versal devices contains high performance ARM A72 processors. On-chip and cache memory are included along with a suite of hardened communication peripherals. In the initial platform, an ARM A72 device will be employed and will be given access to 2GBytes of DDR RAM.

- Programmable Logic (PL)

This contains the following main IP:

Network-On-Chip (NoC) Versal devices are designed around a NoC interconnect, which provides high bandwidth communication between different areas of the device. In this Platform NoC will be used to: * Transmit the streaming ethernet data received by the AXI MCDMA to the memory. * Transmit the ethernet data from the memory to the MRMAC via the streaming interface of the AXI MCDMA.

Multi Rate Media Access Control (MRMAC) The MRMAC IP has AXI stream ports at the transmit and receive ends. The ethernet packets are transmitted/received via these AXI streaming ports. It has an AXI-Lite interface for accessing the control information of the IP.

Quad Base Gigabit Transceiver Interface (GTY) The Quad Base GT receives ethernet data from the external world and transmits it to the MRMAC IP. It also takes the Ethernet data from MRMAC and transmits it to the outside world.

AXI Direct Memory Access (AXI-MCDMA) This is a standard AXI Multi Channel Direct Memory Access IP used in the PL. This facilitates the transfer of the Ethernet packets to the MRMAC for MAC processing.

2.2. Software Description¶

The design uses the AXI Ethernet driver present in Linux kernel to configure MRMAC and initialize four lanes to 10G ethernet rates. The driver initializes MCDMA’s S2MM and MM2S channel descriptors and enables them to transfer data to and from system memory. The driver also does interrupt handling when a packet is received or transmitted via DMA.

Note: Please refer https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842485/Linux+AXI+Ethernet+driver for more details.

2.3. Data Flow Sequence¶

- Transmit:

The Ethernet data generated and stored in the memory.

This data is transferred to the MRMAC via AXI MCDMA MM2S interface.

The MRMAC, after processing the packets transmits it to the GTY.

The GTY Transmits this data to the output onto the Ethernet link.

The GTY output is connected to an external NIC. This NIC receives the ethernet packets.

- Receive

The External NIC generated Ethernet packets.

This data is received atthe GT interface.

From the GT, the data is transferred to MRMAC.

The MRMAC sends this data via the streaming interface to the S2MM port of AXI MCDMA.

The AXI MCDMA writes this data onto the memory.

2.4. Design File Hierarchy¶

The reference design zip file has the following contents:

Documentation (html webpages)

Petalinux Board Support Package (BSP)

Pre-built SD card image

Vivado hardware design project

README file

Design sources zip file

Licenses zip file

The design file hierarchy is shown below:

2.5. Licenses¶

The design includes files licensed by Xilinx and third parties under the terms

of the GNU General Public License, GNU Lesser General Public License,

BSD License, MIT License, and other licenses. The design directory includes two

zip file named sources.zip and license.zip containing the complete set of design source files and licenses extracted from

the design source files respectively. You are solely responsible for checking any files you

use for notices and licenses and for complying with any terms applicable to your

use of the design and any third party files supplied with the design.