Vitis™ チュートリアル |

注記: リポジトリの履歴は、容量を少なくするため、2021 年 8 月 20 日に縮小しました。git pull で問題がある場合は、新しいクローンを作ってください。

その他の Vitis デベロッパー ビデオは、ザイリンクス YouTube チャンネルを参照してください。

すべての開発者に新しい設計経験を¶

Vitis™ 統合ソフトウェア プラットフォームは、FPGA、SoC、Versal ACAP などのヘテロジニアス ザイリンクス プラットフォームでエンベデット ソフトウェアおよびアクセラレーション アプリケーションを開発するための環境です。エッジ、クラウド、ハイブリッド計算アプリケーションをアクセラレーションする統合プログラミング モデルが提供されます。

ハイレベル フレームワークとの統合に使用したり、アクセラレーションされたライブラリを使用して C、C++、Python で開発したり、RTL ベースのアクセラレータおよび下位レベルのランタイム API を使用して、インプリメンテーションをより詳細に制御できます。抽象度のレベルは、選択できます。

チュートリアル¶

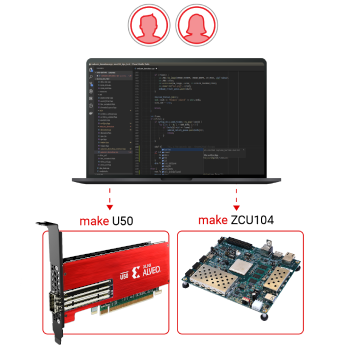

Vitis チュートリアルでは、すべてのザイリンクス プラットフォームでアクセラレーションされたアプリケーションを運用する設計手法およびプログラミング モデルを使用して説明します。

アクセラレーション チュートリアル¶

Vitis コア開発キットを使用して、C++、OpenCL、さらには Verilog や VHDL などの下位レベルのハードウェア記述言語 (HDL) で開発されたアクセラレーション アルゴリズムをビルド、解析、最適化する方法を説明します。

Vitis 高位合成 (HLS)、コンパイラ、アナライザー、デバッガーを使用してパフォーマンスのボトルネックを特定し、Alveo™ データセンター アクセラレーション カードを使用してアルゴリズムの効率とパフォーマンスを向上させる方法について説明します。

AI エンジン開発¶

ザイリンクス初の ACAP (Adaptive Compute Acceleration Platform) デバイスである Versal™ を開発するための Vitis コア ツールの使用方法を説明します。

Versal の AI エンジン アレイと PL IP/カーネルおよびエンベデッド プロセッサ上で動作するソフトウェア アプリケーションを組み合わせて使用し、高度なアルゴリズムをターゲットにし、開発、運用する方法について説明します。

プラットフォーム作成チュートリアル¶

独自のボードをターゲットにしたカスタム プラットフォームのビルド方法と、既存のプラットフォームの変更と拡張方法について説明します。

プラットフォームのハードウェア ソースの設定方法、ランタイム ソフトウェア環境の構築方法、ソフトウェアおよびハードウェア エミュレーションのサポートの追加方法などを説明します。

Vitis 開発者の寄稿チュートリアル¶

Vitis チュートリアルのリポジトリは、ザイリンクスのチームによってのみ管理されるものではありません。皆様のご寄稿を歓迎します。エンド ツー エンドのデザインでも、ヒントや手法などの説明でもかまいません。なんでもほかのユーザーの助けになります。詳細をさらに確認し、ほかの開発者が共有した内容を確認してください。

その他の Vitis チュートリアル リポジトリ¶

機械学習チュートリアル¶

Vitis、Vitis AI、および Vitis アクセラレーション ライブラリを使用して、純粋なソフトウェア定義フローを使用して完全なエンド ツー エンドのアクセラレーションされたアプリケーションをインプリメントする方法を学びます。ハードウェアの専門知識は必要ありません。

Tensorflow フレームワークを使用してザイリンクス ハードウェアをコンフィギュレーションするには、Vitis AI を使用します。Vitis AI を使用すると、ユーザーは推論モデルを数分で量子化、コンパイル、運用できます。

エンベデッド デザイン チュートリアル¶

ザイリンクス適応型 SoC と MicroBlaze™ ソフト プロセッサで、エンベデッド オペレーティング システムとドライバーを構築して使用する方法を説明します。これらのチュートリアルでは、ザイリンクスの提供するオープンソース オペレーティング システムとベアメタル ドライバー、コンパイラ、デバッガー、および従来の SoC ソフトウェア開発用のプロファイリング ツールについて説明します。

Vitis Model Composer チュートリアル¶

Vitis Model Composer を使用した迅速な設計方法について学習します。Vitis Model Composer は、パフォーマンス用に最適化されたブロックのライブラリと、ザイリンクス デバイスへの DSP アルゴリズムのインプリメンテーションを提供します。Vitis Model Composer の AI エンジン、高位合成、および HDL ライブラリを Simulink環境内で使用すると、アルゴリズムをすばやく確認し、プロダクションまでの過程を短縮できます。

Copyright© 2021 Xilinx