Vitis フロー 101¶

カーネル開発、ホスト ソフトウェアの作成、エミュレーション、インプリメンテーション、解析などの Vitis ワークフローの概要。

Vitis がソフトウェア、アクセラレーション、ML 開発を単一の開発プラットフォームで統合する方法について説明します。

Vitis は、データセンターまたはエンベデッド プラットフォームのいずれかをターゲットとした FPGA アクセラレーション アプリケーションを開発するための統合フローを提供します。このチュートリアルでは、ZCU102 カードと Alveo U200 カードの両方でビルドおよび実行する手順について説明します。これらの手順は、ほかのザイリンクス カードでも簡単に使用できます。

注記

このチュートリアルを実行するには、Vitis 2020.2 以降が必要です。

チュートリアル |

内容 |

|---|---|

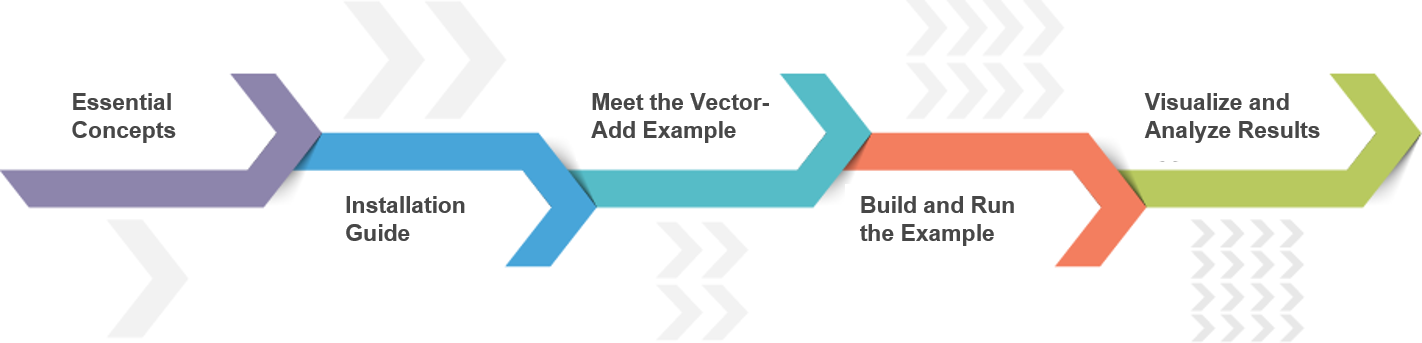

Vitis FPGA アクセラレーション フローの基本的な概念を 10 分以内で説明します。 |

|

Vitis ツール、プラットフォーム、およびランタイム ライブラリのインストール手順を説明します。 |

|

残りのチュートリアルで使用される vector-add 例のソース コードについて説明します。 |

|

アクセラレーション カードでのコンパイル、リンク、および実行に必要なコマンドについて説明します。 |

|

Vitis アナライザーの概要と解析レポートの開き方と解析方法について説明します。 |