Vitis™ アプリケーション アクセラレーション チュートリアル |

4.DATAFLOW 最適化の確認¶

前の手順では、DCT アルゴリズムを最適化して、パイプライン処理済みループを使用して II=1 を達成するさまざまな方法について説明しました。この手順では、DATAFLOW 指示子を使用して関数またはループのタスク レベルの並列処理をイネーブルにします。詳細は、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) の Vitis HLS フローの set_directive_dataflow を参照してください。

DATAFLOW 最適化では、ループ レベルの並列処理に加え、コード内のさまざまな関数間にタスク レベルの並列処理が可能な限り作成されます。

新規ソリューションの作成¶

Vitis 統合ソフトウェア プラットフォームの資料 (UG1416) の Vitis HLS フローの追加のソリューションの作成に示すように、複数のソリューションを作成することで、さまざまなデザイン最適化方法を試すことができます。この演習では、新しいソリューションを作成して DATAFLOW 最適化を使用してみます。

[Explorer] ビューで最上位プロジェクト (

dct_prj) を選択します。右クリックし、[New Solution] をクリックします。

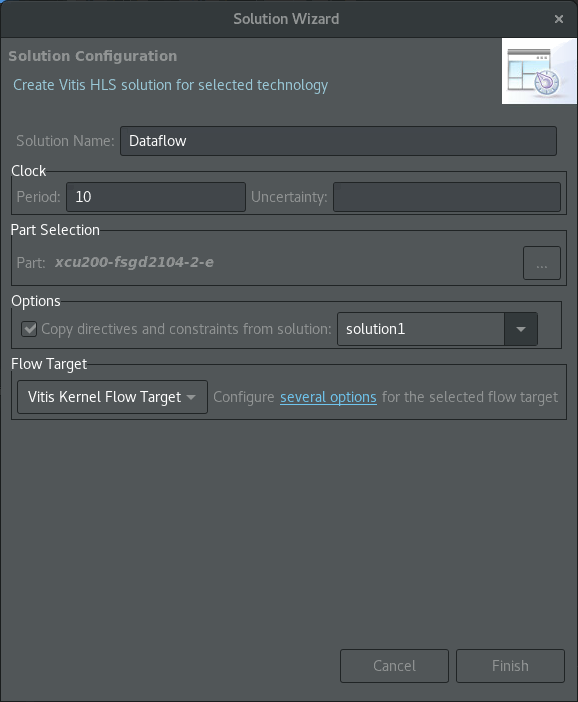

[Solution Wizard] ダイアログ ボックスが開きます。

次のように選択します。

[Solution Name] フィールドに

DATAFLOWと入力します。[Options] で、[Copy directives and constraints from solution] チェック ボックスをオンにして、

solution1を選択します。その他の設定は、デフォルトのままにします。

[Finish] をクリックして新しいソリューションを作成します。

ヒント: 新規ソリューションを作成すると、それがアクティブ ソリューションとして設定され、シミュレーション、合成、その他のコマンドすべてがそのソリューションを使用して実行されます。アクティブ ソリューションは、[Explorer] ビューでソリューションを右クリックし、[Set Active Solution] をクリックすると変更できます。

DATAFLOW 最適化の追加¶

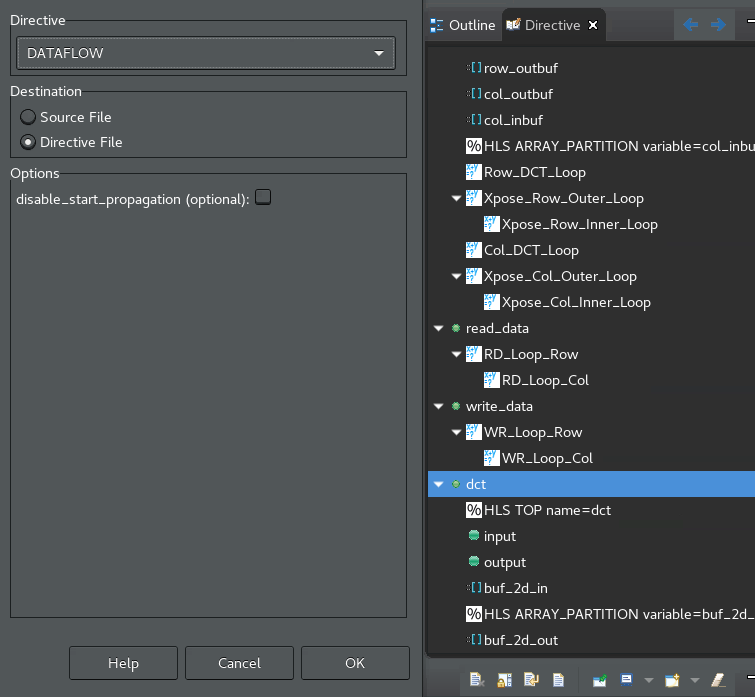

dct.cppタブをクリックしてコード エディターをアクティブにします。[Directive] ビューで最上位の

dct関数を選択して右クリックし、[Insert Directive] をクリックします。[Vitis HLS Directive Editor] が開きます。

次のように選択します。

[Directive] フィールドで [DATAFLOW] を選択します。

[Destination] フィールドで [Directive File] を選択します。

[OK] をクリックして閉じて、指示子を適用します。

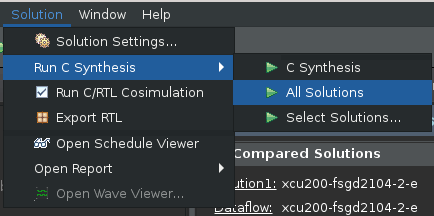

メイン メニューから [Solution] → [Run CSynthesis] → [All Solutions] をクリックして合成を再実行します。すべてのソリューションに対して合成が実行され、結果を比較できます。

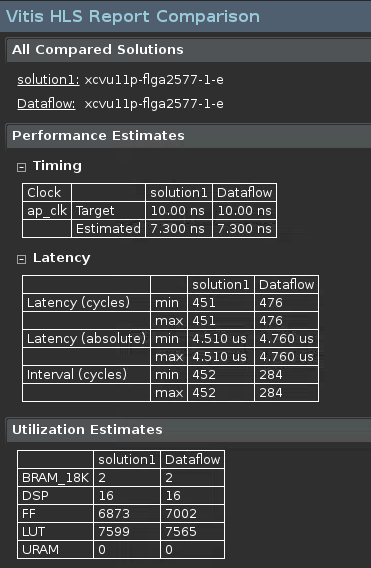

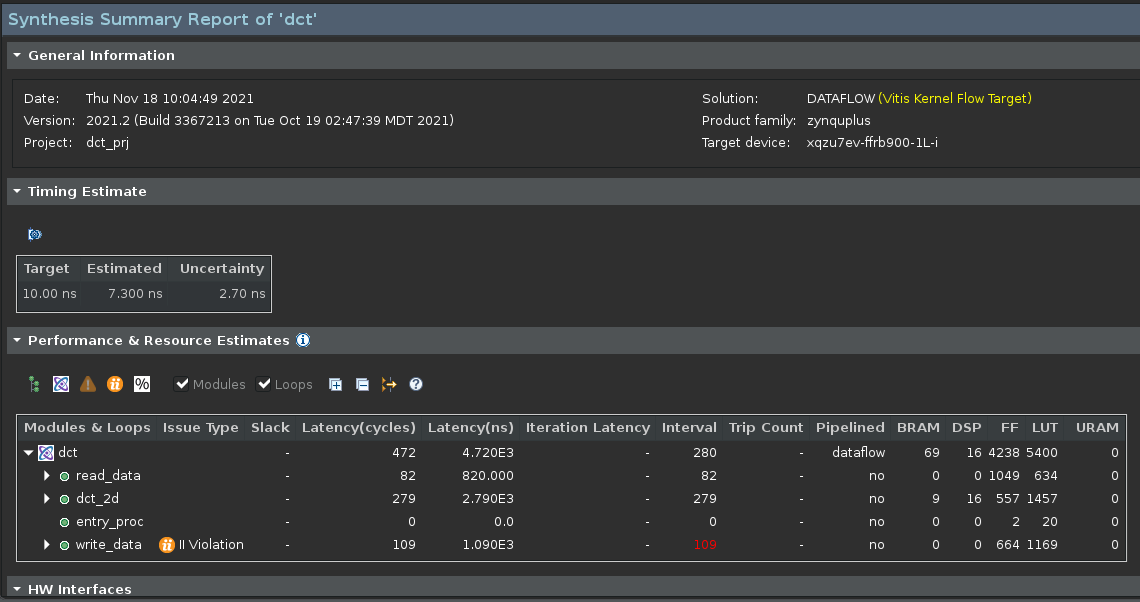

合成が終了すると、アクティブ ソリューション (この場合は DATAFLOW ソリューション) の合成サマリ レポートが表示されます。次の図に示す [Vitis HLS Report Comparison] も表示され、合成されたすべてのソリューションの合成結果が表示されます。

この比較結果から、DATAFLOW ソリューションの開始間隔 (II) が最初のソリューションの約 65% になったことがわかります。これは、DATAFLOW 最適化によるタスク レベルの並列処理の主な利点です。また、デザインの FF および LUT の使用量の見積もりが増加しています。これらはあくまでも見積もりなので、Vivado 合成およびインプリメンテーションのいずれかまたは両方を実行して、より正確なリソース使用量を取得する必要があります。

次の図に、DATAFLOW ソリューションの合成サマリ レポートを示します。

データフロー グラフの表示¶

Vitis HLS には、[Analysis] パースペクティブの機能の 1 つとしてデータフロー グラフも提供されています。DATAFLOW 最適化は、必要なパフォーマンス データを提供する C/RTL 協調シミュレーション完了後にのみ理解可能になる動的最適化です。合成後は、協調シミュレーションを実行する必要があります。詳細は、『Vitis 統合ソフトウェア プラットフォームの資料 』(UG1416) の Vitis HLS フローの Vitis HLS での C/RTL 協調シミュレーションを参照してください。

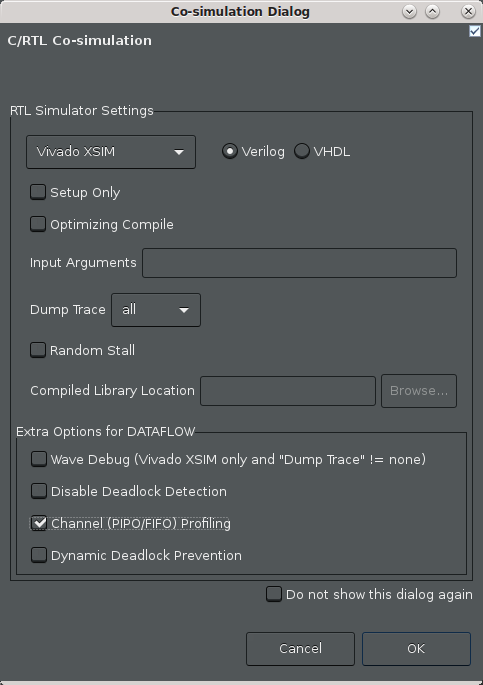

メニューから [Solution] → [Run C/RTL Co-Simulation] をクリックします。[Co-simulation Dialog] ダイアログ ボックスが表示されます。

次のように選択します。

[Channel (PIPO/FIFO) Profiling] をオンにします。

[OK] をクリックします。

協調シミュレーションが終了すると、協調シミュレーション レポートが開き、シミュレーション テストベンチが問題なく実行されたかどうかが表示されます。データフロー解析では、テストベンチが合成済み関数を複数回呼び出して、複数のイテレーションからパフォーマンス データを取得し、FIFO をフラッシュします。パフォーマンスに関しては、1 つの関数呼び出しでレイテンシ、その関数への 2 つ以上の呼び出しで II (開始間隔) が計算されます。

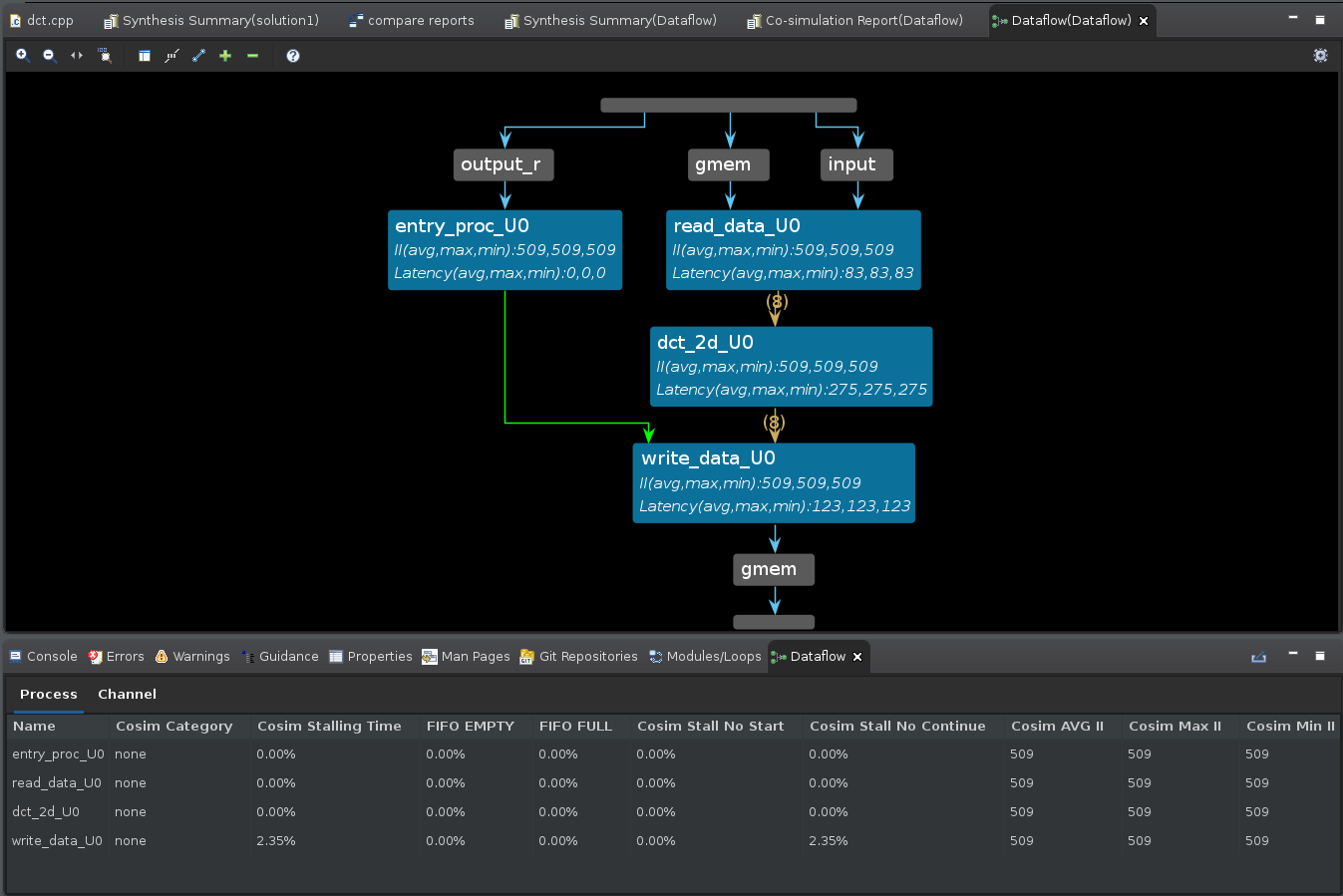

シミュレーションが完了したら、[Solution] → [Open Dataflow Viewer] をクリックして、次のようなビューアーを開きます。

ヒント: デザインにデータフロー グラフが含まれるかどうかは、[Explorer] ビューまたは [Synthesis Summary] でプロジェクトに

アイコンがあるかどうかでわかります。

アイコンがあるかどうかでわかります。[Dataflow] ビューには、関数とその関数を介するフローが表示されます。C/RTL 協調シミュレーションを実行すると、グラフのパフォーマンス データが書き込まれ、グラフの下の [Process] および [Channel] の表にもデータが挿入されます。協調シミュレーションからのパフォーマンス データがない場合、グラフおよび表には値が存在しないことを示す「NA」と表示されます。詳細は、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) の Vitis HLS フローの Dataflow Viewer を参照してください。

データフロー ビューアーでは、次のスループット解析オプションが使用されます。

グラフには、DATAFLOW 領域の全体的なトポロジが表示され、どのタイプのチャネル (FIFO/PIPO) が DATAFLOW 領域のタスク間通信のために推論されたかが示されます。各チャネルおよびプロセスを解析すると、デッドロックや FIFO のサイズが適切でないためにスループットが小さいなどの問題を解決するのに役立ちます。

協調シミュレーションのデータがあると、シミュレーション過程で FIFO の最大サイズを確認することにより、FIFO のサイズを決定する際の基準となるので、FIFO サイズの問題を解決できます。また、協調シミュレーションでは、自動デッドロック検出により、デッドロックに関係するプロセスおよびチャネルがハイライトされるので、問題をすばやく見つけて修正できます。

協調シミュレーション後にレポートされるデータには、FIFO のサイズだけでなく、プロセスおよびチャネルごとに、入力を待っていたり、出力の書き込みがブロックされたりしているストール時間も示されます。このグラフがあると、これらの問題を理解し、プロデューサーが高速でコンシューマーが高速 (またはその逆) の状況に対処するためチャネルのサイズをどのように管理すればよいかを判断するのに役立ちます。また、DATAFLOW 領域の真ん中で入力から読み出すことがパフォーマンスにどのように影響するかを理解するのにも有益です。これがパフォーマンスに影響する状況はよくあります。

指示子のプラグマへの変換¶

デザインを最適化したので、Tcl スクリプトの指示子 (Vitis HLS ツールが実行) をソース コードのプラグマに変換して、その他のユーザーやデザイン チームと共有し、Vitis 統合ソフトウェア プラットフォーム内で使用できるようにします。[Directive] ビューで指示子を選択し、次のプロセスを使用してプラグマに変更します。

dct.cppタブをクリックしてコード エディターをアクティブにするか、必要であればソース コードを開きます。[Directive] ビューをスクロールダウンして指示子を右クリックし、[Modify Directive] をクリックします。[Vitis HLS Directive Editor] が表示されます。

[Vitis HLS Directive Editor] で [Destination] を [Source File] に変更し、[OK] をクリックします。これで指示子がプラグマに変更されてソース コード ファイルに記述されます。これは、

dct.cppソース ファイルで確認できます。col_inbuf変数のARRAY_PARTITION指示子を変更すると、col_inbuf変数が見つからないので、関数の 1 行目にプラグマを挿入することを示す警告メッセージが表示されます。[OK] をクリックしてプラグマを挿入します。プラグマの配置は、

dct.cppファイルの#pragma HLS ARRAY_PARTITION...行を切り取って、42 行目のcol_inbuf変数の定義の後に貼り付けて、手動で修正する必要があります。プラグマは変数の後に定義しないと、コンパイラで正しく関連付けられません。このようにしておかないと、Vitis HLS でコードをコンパイルする際にエラー メッセージが表示されます。指示子をプラグマに変換したので、最適化がコードに含まれるようになり、

dct.cppコードが移植可能になりました。[File] → [Save As] をクリックして、プラグマを含む

dct.cppファイルを./vitis_hls_analysis/reference-filesフォルダーに保存します。このファイルは次の演習で使用できます。

Vitis カーネルのエクスポート¶

最後に、高位合成の結果を合成済みカーネル (.xo) ファイルとしてエクスポートできます。

メイン メニューから [Solution] → [Export RTL] をクリックします。[Export RTL] ダイアログ ボックスが開きます。

[Format Selection] で [Vitis Kernel (.xo)] を選択します。

[Output location] フィールドで

dct.xoファイルを書き込む./vitis_hls_analysis/reference-filesフォルダーを指定します。[OK] をクリックしてカーネルをエクスポートします。

まとめ¶

このチュートリアルでは、次のことを学びました。

Vitis HLS ツールで C/C++ コードを最適化し、Vitis アプリケーション アクセラレーション開発フローで使用できるように RTL コードに合成しました。

コードを最適化した後、Vitis アプリケーション プロジェクトで使用できるよう、コンパイル済みカーネル オブジェクト (

.xo) をエクスポートしました。

これらは、Vitis および Vitis HLS ツールを使用してアプリケーションおよび関数をビルドしてアクセラレーションする要素です。Vitis アプリケーション プロジェクトでは、RTL カーネル オブジェクト (.xo) を含む Vitis HLS カーネルとコンパイルされていない C/C++ カーネル コード (.c/.cpp) を混合して、より複雑なアクセラレーション アプリケーションを作成できます。

このチュートリアルでは、前の演習で最適化したコンパイルされていない C++ コード (dct.cpp) を作成しました。必要に応じて HLS カーネル オブジェクトを削除し、Vitis アプリケーション プロジェクトにこの最適化済み C++ コードを追加できます。その場合、Vitis IDE で C++ カーネル コードをコンパイルする際に、ビルド プロセスの一部として Vitis HLS が呼び出されます。

Copyright© 2022 Xilinx