Vitis™ アプリケーション アクセラレーション開発フロー チュートリアル |

Vitis フローを使用した Alveo での GT ーネルの使用¶

バージョン: Vitis 2022.1

ザイリンクス Alveo データセンター アクセラレータ カードには、カードによって 1 つまたは 2 つの QSFP28 ポートなどのネットワーク接続が含まれます。QSFP28 インターフェイスでは、10GbE、25GbE、40GbE、100GbE などのさまざまなイーサネット設定がサポートされています。1 つのレーンのイーサネット プロトコルを複数インスタンシエーションすることも可能です。Vitis フローと最新のプラットフォームを使用すると、GTY トランシーバーを含む RTL カーネルを作成でき、HLS 計算ユニットを含むその他のカーネルへのストリーミング接続、DRAM メモリへのデータパス バッファリング、Vitis ツールによるホストと FPGA 間のデータ移動用ドライバー アクセスなど、完全に統合されたデザインを実現するための機能が提供されます。

このチュートリアルでは、GTY トランシーバーを RTL カーネルに含め、Vitis を使用してトップレベルのハードウェア オーバーレイ デザインに統合する手順を説明します。Alveo U200 カードを例にしていますが、同様の手順をほかの Alveo カードにも簡単に適用できます。このチュートリアルのサンプル デザインは、現実的な機能を持たず、ここでは方法を示すためだけに使用されています。ここでは、2 つのレーン番号設定 (x1 および x4) を用意しています。

機能とデザインの概要¶

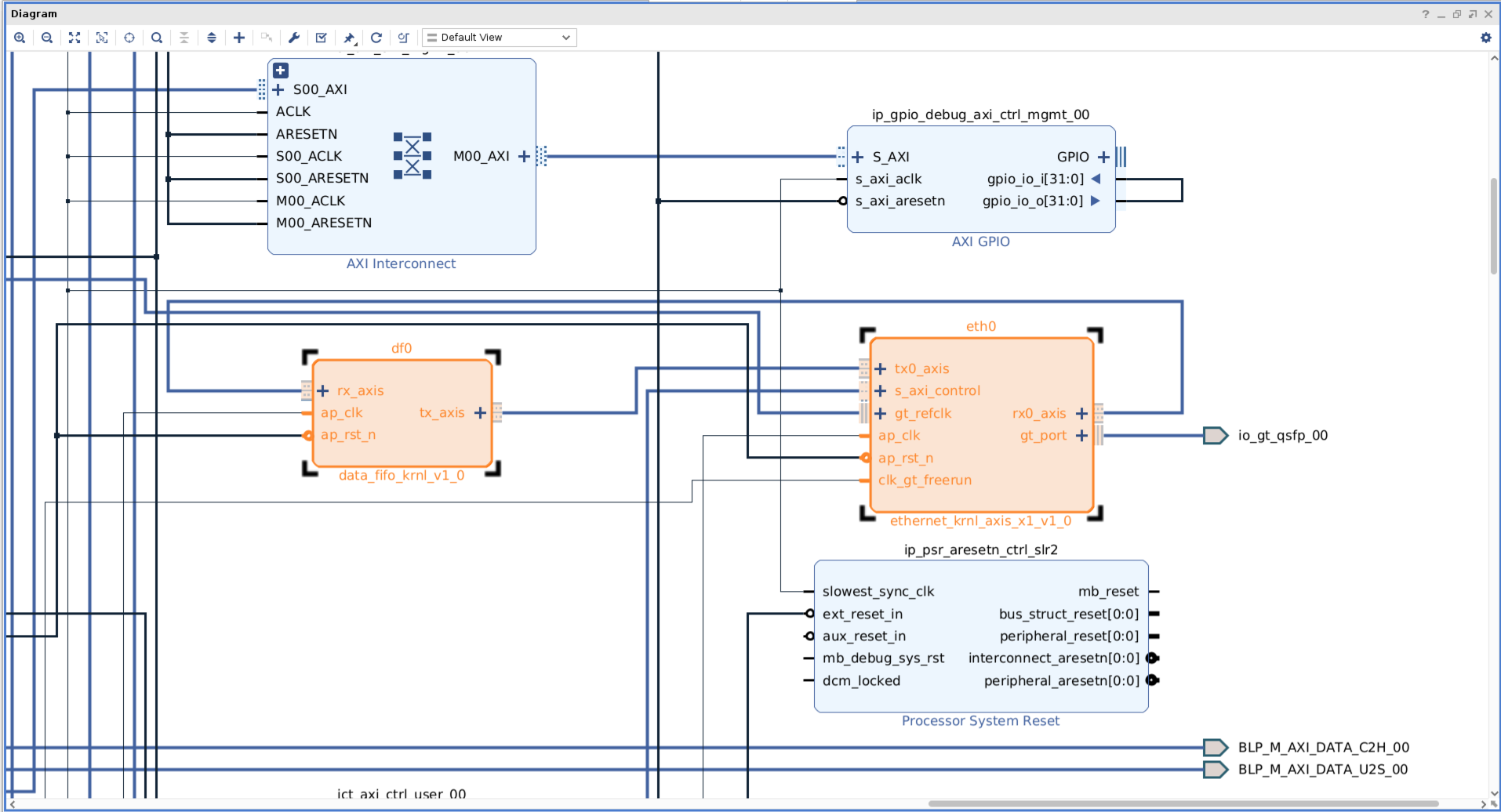

次は、2 つの RTL カーネルで構成されるデザインのブロック図です。

ethernet_krnl_axis_x1/4: このカーネルには、1 つのシングル チャンネルまたは 4 チャンネルの 10G イーサネット サブシステム IP、1 つの AXI 制御スレーブ、2 つまたは 8 つの AXI ストリーム データ FIFO モジュールが含まれます。GT トランシーバーとの間では、データが AXI ストリーム データ FIFO にストリーミングされ、外部に接続されます。カーネルは XRT の ap_ctrl_hs の実行モデルを使用します。ホスト プログラムは、AXI 制御スレーブを介してイーサネット IP を制御できます。

data_fifo_krnl: このカーネルには 2 つの AXI ストリーム データ FIFO モジュールが含まれており、これらは一緒に接続されて外部 AXI ストリーム ポートへのループバック データパスを形成します。カーネルは XRT の ap_ctrl_none を使用します。

トップ レベルのハードウェア トポロジでは、これら 2 つまたは 5 つのカーネル (レーン番号に依存) が AXI ストリーム接続を介してスティッチングされます。また、ethernet_krnl_axis_x1/4 カーネルの AXI 制御スレーブもプラットフォームに接続されています。GT トランシーバー用のこれらを含む必要なリセット信号とクロック信号は、プラットフォームの提供する関連リソースに接続されます。

前述のように、この設計トポロジから意味のある機能はないので、ホスト プログラム コードは提供されていません。

デザイン フローとチュートリアルの手順¶

まず、次に示すこのチュートリアルの重要なファイルを確認してください。

.

├── connectivity_x1/4.cfg Vitis linking configuration file

├── gen_ip_x1/4.tcl Vivado script to generate IP

├── Makefile Makefile for every steps

├── pack_data_fifo_kernel.tcl Vivado script to pack data fifo kernel

├── pack_eth_x1/4_kernel.tcl Vivado script to pack ethernet kernel

└── rtl/ RTL sources code for two kernels

この 2 つのカーネルの RTL ラッパー ファイルは、./rtl ディレクトリに含まれています。すべての手順はコマンドライン インターフェイスで実行され、そのフローを制御するために Makefile が使用されます。Makefile の次の行では、Alveo U200 をデザインのターゲット カードとして指定していますが、ほかの Alveo カード用に変更することもできます。また、レーン番号の設定も変更できます (デフォルトは 1)。

# Target hardware setting, uncomment appropriate lines

BOARD := u200

PLATFORM := xilinx_u200_gen3x16_xdma_2_202110_1

PART := xcu200-fsgd2104-2-e

では、チュートリアルのルート パスを入力し、チュートリアルを順を追って説明します。

1.IP の生成¶

前述のように、イーサネット サブシステム (xxv_ethernet) と AXI ストリーム FIFO (axis_data_fifo) の 2 つの IP がデザインに必要です。これらは、Vivado の GUI モードまたは Tcl スクリプトを使用したバッチ モードで生成できます。ここでは、次のコマンドを使用して、Vivado のバッチモードで生成します。

make gen_ipこれにより、Vivado が起動し、Tcl スクリプト gen_ip.tcl が実行されます。生成された IP は、作成された ip_generation ディレクトリに含まれます。Vivado GUI モードを使用している場合は、Tcl スクリプトを確認してダイアログ ボックスの設定を推測できます。IP xxv_ethernet の設定の中には、使用するターゲット Alveo カードに関係するものがあります。

2.カーネルのパッケージ¶

ここでは、RTL デザイン ファイルは既に ./rtl ディレクトリにあるので、IP (.xci files) と共に 2 つの Vitis カーネル (.xo ファイル) にパッケージする必要があります。Vivado GUI バージョンの IP パッケージャーを使って IP をパッケージすることはできますが、ここではコマンドラインと Tcl スクリプトを使ってみます。次のコマンドでカーネルをパッケージすると、2 つのカーネル ファイル (ethernet_krnl_axis_x1.xo および data_fifo_krnl.xo) が、その後の Vitis リンキング ジョブ用に生成されます。

make pack_kernelTcl スクリプト pack_eth_kernel.tcl および pack_data_fifo_kernel.tcl からは、GUI モードの Vivado ダイアログ ボックスに対応するカーネル パッケージ設定を確認できます。イーサネット カーネルのパッケージ手順では、標準の AXI バス インターフェイスに加えて、後の Vitis v++ 自動接続機能用にさらに 2 つのバス インターフェイス (GT トランシーバーのデータ バス用の gt_port、GT トランシーバーの差動クロック用の gt_refclk) が作成されていることがわかります。

3.Vitis のリンキング¶

ここでは、Vitis v++ ツールを使ってハードウェア リンキングを終了し、.xclbin ファイルを生成します。次のコマンドを実行します。

make build_hwこれにより、 connectivity_x1.cfg をリンキング コンフィギュレーション ファイルとして v++ コマンドが実行されます。コンフィギュレーション ファイルの次の行では、Vitis に xilinx_u200_gen3x16_xdma_1_202110_1 プラットフォームの GT トランシーバー固有の信号を接続するよう指示しています。

# For xilinx_u200_gen3x16_xdma_1_202110_1 platform

connect=eth0/clk_gt_freerun:ss_ucs/aclk_kernel_00

connect=io_clk_qsfp_refclka_00:eth0/gt_refclk

connect=eth0/gt_port:io_gt_qsfp_00

ほかのカードやプラットフォームを使用している場合、信号やポート名が異なる場合がありますので、それに応じて調整する必要があります。これらのプラットフォーム固有の GT 信号/ポート名については、platforminfo コマンドでレポートされるプラットフォーム情報を参照してください。次に例を示します。

platforminfo -p xilinx_u200_gen3x16_xdma_1_202110_1 -v

v++ のリンキング ジョブが終了したら、Vivado GUI で Vivado プロジェクト ./_x/link/vivado/vpl/prj/prj.xpr を開き、ブロック デザイン ulp を開きます。次のスクリーンショットのように、2 つのカーネル (インスタンス名 df0 と eth0) のすべての信号、特に GT トランシーバーの信号が正しく接続されていることがわかります。

v++ のリンキングが終了すると、XCLBIN ファイル top_level.xclbin ができます。また、Vivado を使用してプロジェクト ./_x/link/vivado/vpl/prj/prj.xpr を開き、最終的にインプリメントされたデザインを開いて、レポートやシリコン フロアプランを確認することもできます。

サマリ¶

Vitis フローで Alveo カードに GTY トランシーバーを使用するのは、非常にシンプルで簡単です。通常の RTL カーネルとして処理して、GT トランシーバー固有の信号用の特別な設定をするだけです。Vitis の強力で柔軟な機能を使用することで、効率的に統合できるようになっています。