エンベデッド デザイン¶

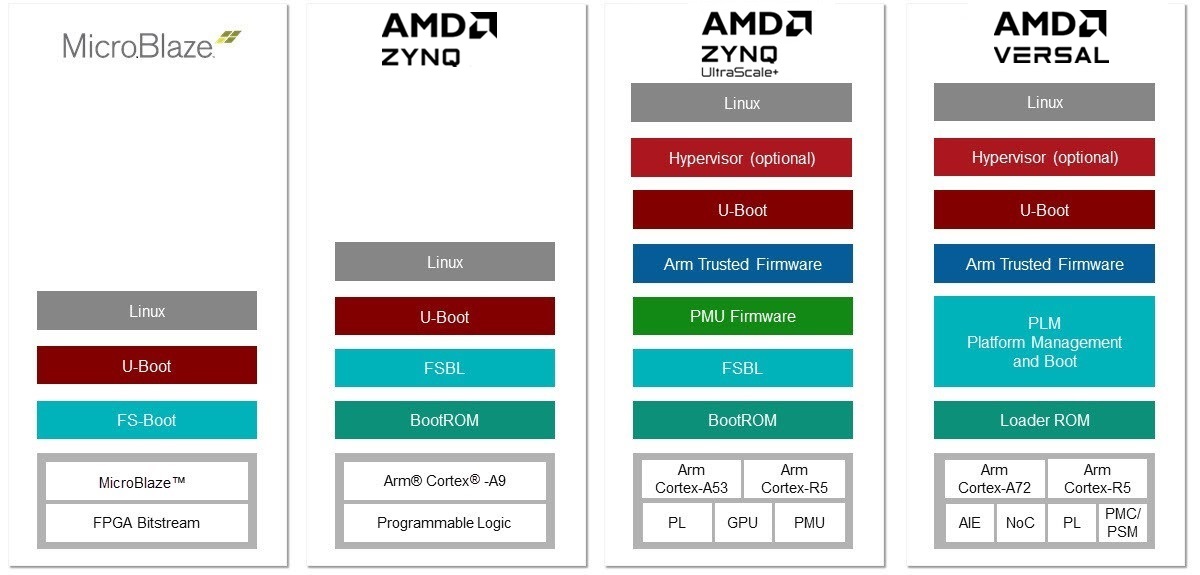

AMD およびそのエコシステム パートナーは、コンセプトからリリースまでを効率的で迅速に移行するエンベデッド ツールおよびランタイム環境を提供しています。AMD Zynq™ SoC および AMD Zynq UltraScale+™ MPSoC デバイス、AMD MicroBlaze™ プロセッサ コア、オープンソース オペレーティング システムやベアメタル ドライバーを含む Arm® Cortex-M1/M3 マイクロ コントローラー、複数のランタイムとマルチ OS 環境、高度な統合開発環境、コンパイラ、デバッガー、およびプロファイリング ツールを使用したエンベデッド システムの作成に必要なすべてのコンポーネントが提供されます。

このリポジトリには、エンベデッド デザインの作成に関する情報が含まれます。含まれる資料は、次のとおりです。

入門チュートリアル¶

チュートリアル |

ボード |

説明 |

|---|---|---|

Versal VMK180/VCK190/VPK180 |

Versal™ VMK180/VCK190/VPK180 評価ボードのエンベデッド開発に AMD Vivado™ Design Suite フローおよび Vitis™ 統合ソフトウェア プラットフォームを使用する方法を説明します。 |

|

ZCU102 Rev 1.0/1.1 |

AMD Zynq™ UltraScale+™ MPSoC デバイスのエンベデッド開発に Vivado Design Suite フローおよび Vitis 統合ソフトウェア プラットフォームを使用する方法を説明します。 |

|

ZC702 Rev 1.0 |

Zynq 7000 SoC デバイスのエンベデッド開発に Vivado Design Suite フローおよび Vitis 統合ソフトウェア プラットフォームを使用する方法を説明します。 |

機能チュートリアル¶

チュートリアル |

説明 |

|---|---|

First Stage Boot Loader (FSBL) は SoC デバイスを初期化し、必要なアプリケーションまたはデータをメモリに読み込んで、ターゲット CPU コアでアプリケーションを起動できます。FSBL は Vitis プラットフォーム プロジェクトに含まれますが (プラットフォーム プロジェクトの作成中にブート コンポーネントの作成を有効にした場合)、追加の FSBL アプリケーションを汎用アプリケーションとして作成して、さらに変更またはデバッグできます。 |

|

Vivado IP インテグレーターを使用して、Spartan™ 7 FPGA 用のシンプルな MicroBlaze™ システムを作成します。 |

|

スタンドアロンのドメインまたはボード サポート パッケージ (BSP) と、Linux のブートおよび Vitis ソフトウェア プラットフォームでのデバックで作成した AXI CDMA に関連するアプリケーションのプロファイリング機能を有効にします。 |

設計チュートリアル¶

チュートリアル |

説明 |

|---|---|

Zynq UltraScale+ MPSoC デバイスの GPU と DP をベースとしたデザインを実行するために必要な設定、パッケージ、およびツール フローを示します。 |

デバッグ¶

チュートリアル |

説明 |

|---|---|

エンベデッド ソフトウェアのデバッグの具体例を紹介し、さまざまなザイリンクス デバッグ機能がどのように役立つかを説明します。 |

ユーザー ガイド¶

チュートリアル |

説明 |

|---|---|

パフォーマンス解析ツールボックスの技術的な詳細と、その利便性および機能を活用するための手法を説明します。 |

|

Versal Dhrystone ベンチマーク (英語版) |

Dhrystone ベンチマークのリファレンス デザインを生成し、Dhrystone アプリケーションを構築および実行する手順を示します。 |