2020.1 Vitis™ アプリケーション アクセラレーション開発フロー チュートリアル2019.2 Vitis アプリケーション アクセラレーション開発フロー チュートリアル |

IP/XO パッケージ フロー¶

この演習で説明するプロセスは、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) のアプリケーション アクセラレーション開発フローの RTL カーネルの開発フローに説明されている IP/XO パッケージ フローに従っています。

重要: チュートリアルのコマンドを実行する前に、『Vitis 統合ソフトウェア プラットフォームの資料』 (UG1416) のアプリケーション アクセラレーション開発フローの Vitis 環境の設定に説明されているように、次のコマンドを実行してツール環境を設定する必要があります。

#setup Xilinx Vitis tools. XILINX_VITIS and XILINX_VIVADO will be set in this step. source <VITIS_install_path>/settings64.sh #Setup Xilinx runtime. XILINX_XRT will be set in this step. source <XRT_install_path>/setup.sh

新規プロジェクトの作成¶

ターミナル ウィンドウに

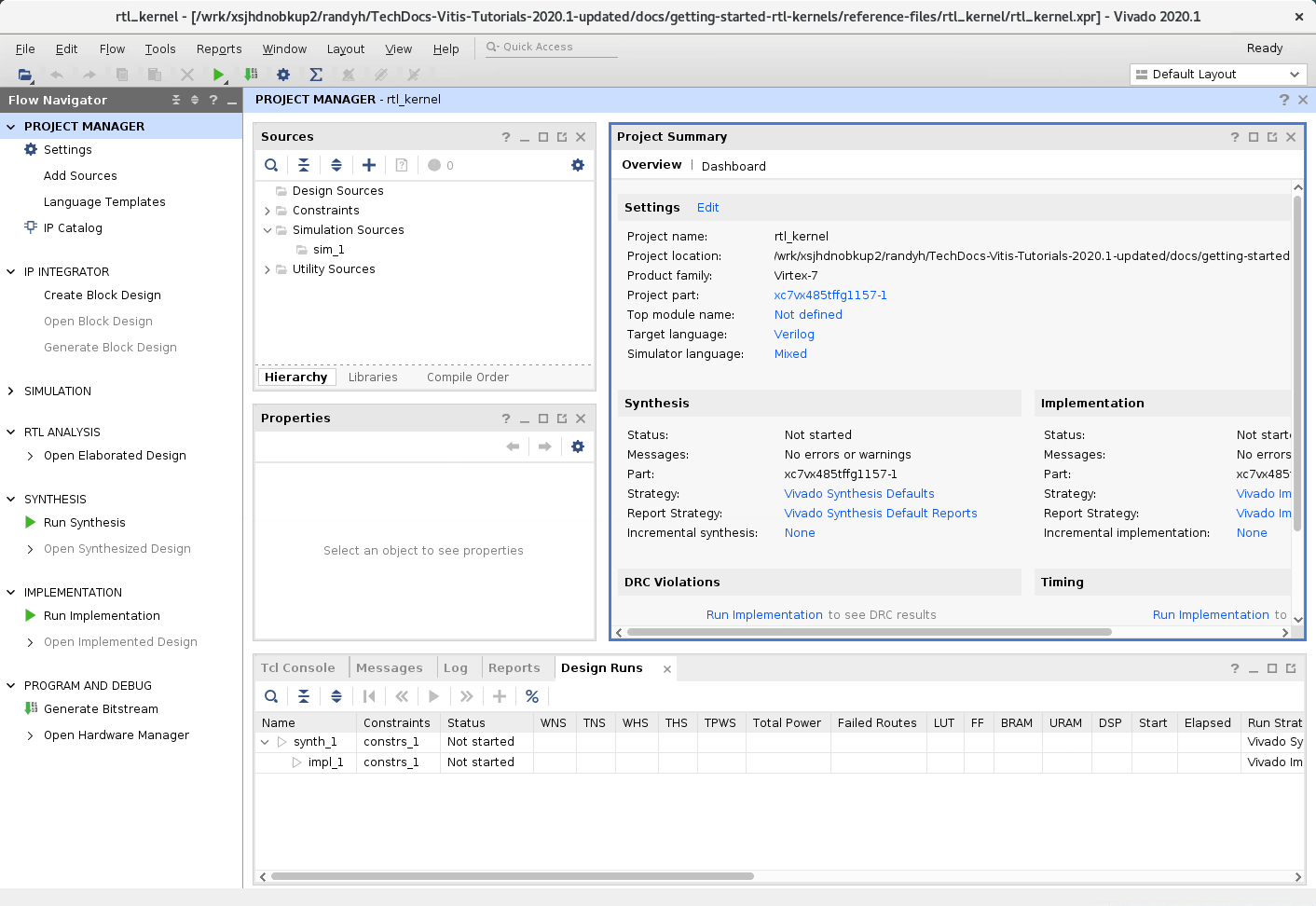

vivadoコマンドを入力して Vivado® IDE を起動します。[Create Project] をクリックするか、[File] → [Project] → [New] をクリックします。

New Project ウィザードが開きます。

[Next] をクリックします。

New Project ウィザードの [Project Name] ページで、次のように設定します。

[Project name] にプロジェクト名 (

rtl_kernelなど) を入力し、[Project location] でプロジェクト ディレクトリを指定します。[Create Project subdirectory] チェック ボックスをオンにします。

[Next] をクリックします。

[Project Type] ページで、次のように設定します。

[RTL Project] をオンにします。

[Do not specify sources at this time] をオンにします。

[Next] をクリックします。

[Default Part] ページで [Boards] を選択し、[Search] フィールドに「

U200」と入力します。[Alveo U200 Data Center Accelerator Card] を選択し、[Next] をクリックします。

[New Project Summary] ページが表示されます。

プロジェクトの詳細を確認し、[Finish] をクリックしてプロジェクトを作成します。

Vivado IDE に作成した新規プロジェクトが開きます。

カーネル ソースの追加¶

次に、プロジェクトに RTL ファイルを追加し、IP としてパッケージします。このチュートリアルでは RTL ファイルは提供されていますが、実際にはこの時点で独自の RTL コードを挿入します。

[Sources] ウィンドウで [Add Sources] ボタン (![[Add Sources] ボタン](./images/icon_add_sources.png)) をクリックします。[Add Sources] ダイアログ ボックスが開きますます。

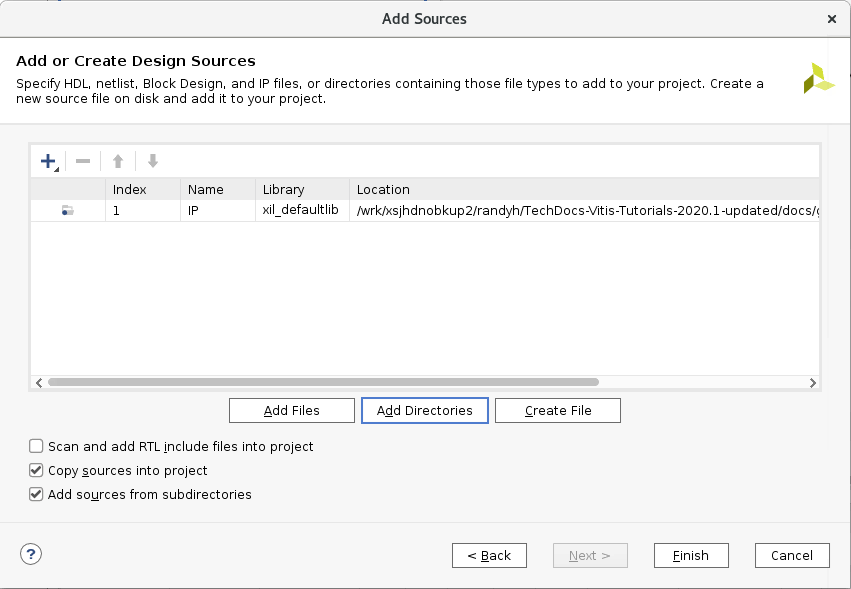

[Add or create design sources] をオンにし、[Next] をクリックします。

[Add Directories] をクリックし、

reference-files/srcのIPディレクトリ (RTL ソースを含む) を選択します。注記: ユーザーの RTL IP を追加するには、それに必要なフォルダーまたはファイルを指定します。

[Copy sources into project] および [Add sources from subdirectories] をオンにします。

[Finish] をクリックします。

ファイルがプロジェクトに追加され、Vivado Design Suite で

Vadd_A_B.vがデザインの最上位ファイルとして認識されます。この RTL モジュールには、概要で説明されている RTL カーネルのハードウェア インターフェイス要件と互換性のあるインターフェイスが含まれます。これは、[Sources] ウィンドウでファイルをダブルクリックしてコード エディター ウィンドウで開くと、Vadd_A_Bモジュール定義に含まれます。module Vadd_A_B #( parameter integer C_S_AXI_CONTROL_ADDR_WIDTH = 12 , parameter integer C_S_AXI_CONTROL_DATA_WIDTH = 32 , parameter integer C_M00_AXI_ADDR_WIDTH = 64 , parameter integer C_M00_AXI_DATA_WIDTH = 512, parameter integer C_M01_AXI_ADDR_WIDTH = 64 , parameter integer C_M01_AXI_DATA_WIDTH = 512 )

IP パッケージャーを開く¶

ファイルをプロジェクトに追加したので、カーネルとして使用する IP をパッケージできます。

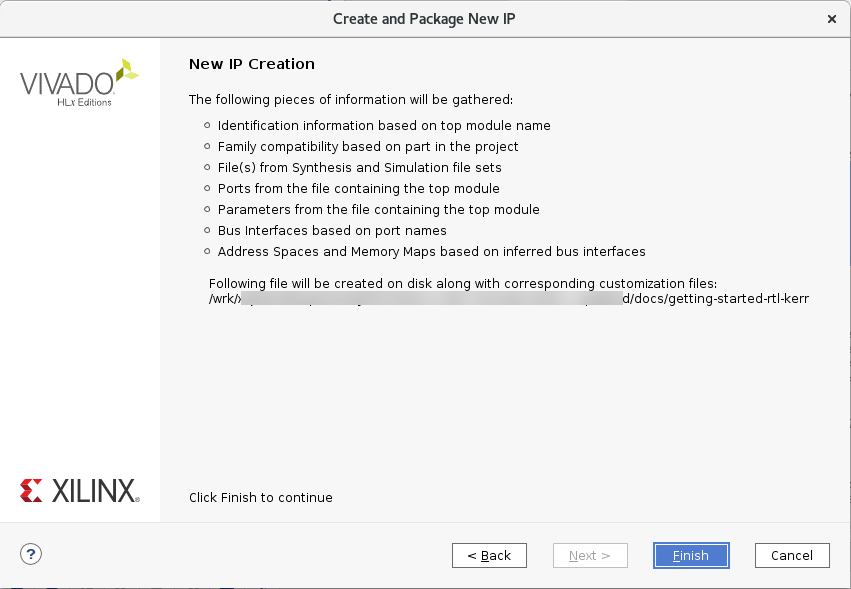

[Tools] → [Create and Package New IP] をクリックします。

[Next] をクリックします。

[Package your current project] をオンにして [Next] をクリックします。

[IP location] で IP がパッケージされるデフォルト ディレクトリを確認します。後の手順で

package_xoコマンドを実行する際は、このディレクトリを変更する必要があります。[Next] をクリックします。サマリ ページが表示されます。

サマリを確認し、[Finish] をクリックします。

[Package IP] ウィンドウが表示されます。

![[Package IP] ウィンドウ](./images/package_ip_interface.png)

ポートおよびインターフェイスの編集¶

[Packaging Steps] の下から [Ports and Interfaces] を選択します。[Ports and Interfaces] ページが表示されます。

m00_axiインターフェイスを右クリックし、[Associate Clocks] をクリックします。[Associate Clocks] ダイアログ ボックスが開き、使用可能なクロックのリストが表示されます。この場合、AXI インターフェイスに関連付ける

ap_clkインターフェイスのみがリストされます。ap_clkを選択し、[OK] クリックします。プロセスを繰り返し、

ap_clkをm01_axiインターフェイス、s_axi_controlインターフェイスに関連付けます。次に、

FREQ_HZパラメーターをap_clkに追加します。[Ports and Interfaces] ウィンドウで [Clock and Reset Signals] を展開します。

ap_clkインターフェイスを右クリックし、[Edit Interface] をクリックします。[Edit Interface] ダイアログ ボックスが表示されます。[Parameters] タブをクリックします。

左側のペインで [Requires User Setting] を展開し、

FREQ_HZパラメーターを選択して [Move selected parameters to the right] (右方向矢印) をクリックします。

![[Edit Interface] ダイアログ ボックス](./images/edit_interface.png)

[OK] をクリックして、[Edit Interface] ダイアログ ボックスを閉じます。

RTL カーネルには、値の競合の解決方法を指定するため、

FREQ_HZパラメーターにvalue_resolve_typeプロパティも必要です。[Tcl Console] ウィンドウで次のコマンドを使用して、このプロパティの値をuserに設定します。set_property value_resolve_type user [ipx::get_bus_parameters -of [::ipx::get_bus_interfaces -of [ipx::current_core] *clk*] "FREQ_HZ"]

制御レジスタおよびアドレス オフセットの追加¶

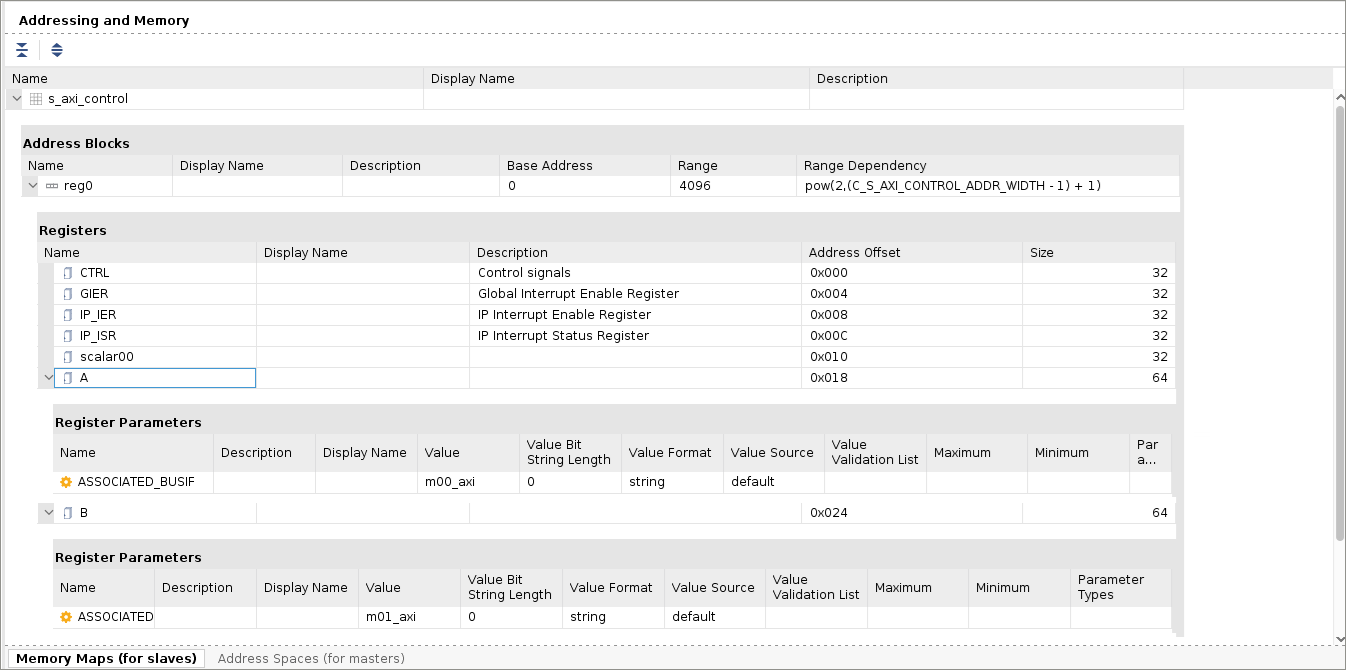

デザインのインターフェイスには、制御レジスタとアドレス オフセットも追加する必要があります。これは、[Package IP] ウィンドウの [Addressing and Memory] ページで実行します。 次の属性の制御レジスタを追加する必要があります。

| 名前 | 説明 | オフセット | サイズ (ビット数) |

|---|---|---|---|

| CTRL | 制御信号 | 0x000 | 32 |

| GIER | グローバル割り込みイネーブル レジスタ | 0x004 | 32 |

| IP_IER | IP 割り込みイネーブル レジスタ | 0x008 | 32 |

| IP_ISR | IP 割り込みステータス レジスタ | 0x00C | 32 |

| scalar00 | スカラー値 | 0x010 | 32 |

| A | ポインター引数 | 0x018 | 64 |

| B | ポインター引数 | 0x024 | 64 |

[Packaging Steps] の下から [Addressing and Memory] を選択します。[Addressing and Memory] ページが表示されます。

[Address Blocks] の下から [reg0] を右クリックし、[Add Reg] をクリックします。

[Add Register] ダイアログ ボックスにレジスタ名を入力し、[OK] をクリックします。

ヒント: CTRL、GIER など、上記の表にリストされているすべてのレジスタを追加する必要があります。[Tcl Console] ウィンドウで次の Tcl コマンドを使用し、必要なレジスタを追加することもできます。

ipx::add_register CTRL [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register GIER [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register IP_IER [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register IP_ISR [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register scalar00 [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register A [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]] ipx::add_register B [ipx::get_address_blocks reg0 -of_objects [ipx::get_memory_maps s_axi_control -of_objects [ipx::current_core]]]

[Addressing and Memory] ページでレジスタを追加したら、説明、オフセット、レジスタのサイズを追加する必要があります。

各レジスタの [Description] フィールドをクリックし、上の表に示す説明を入力します。

[Address Offset] フィールドをクリックし、オフセットを入力します。

[Size] フィールドをクリックし、サイズを入力します。

ヒント: 説明はオプションですが、オフセットとサイズは必須です。

すべてのレジスタの属性を上の表に従って入力したら、各ポインター引数に M_AXI インターフェイスを割り当てる必要があります。

[Registers] の表でレジスタ

Aを右クリックし、[Add Register Parameter] をクリックします。[Add Register Parameter] ダイアログ ボックスで、ASSOCIATED_BUSIF パラメーターを追加して [OK] をクリックします。

このパラメーターは、バス インターフェイスをレジスタに関連付けます。レジスタ

Bに対して、上記の 2 手順を繰り返します。ASSOCIATED_BUSIF の [Value] フィールドに、レジスタ

Aにはm00_axi、レジスタBにはm01_axiと入力します。

整合性のチェック、プロパティの割り当て、および IP のパッケージ¶

[Packaging Steps] の下から [Review and Package] を選択します。[Review and Package] ページが表示されます。

[Tcl Console] ウィンドウで次のコマンドを使用してプロパティを追加します。

set_property xpm_libraries {XPM_CDC XPM_MEMORY XPM_FIFO} $core set_property sdx_kernel true $core set_property sdx_kernel_type rtl $coreこれらのプロパティを追加したら、check_integrity コマンドを再実行します (オプション)。IP のチェックで問題は検出されないはずです。

IP をパッケージする準備ができました。その前に、IP をパッケージしたときにアーカイブ ファイルが生成されるように設定されているかを確認します。

[Review and Package] ページの [After Packageing] セクションを見ます。アーカイブが生成されるように設定されていない場合は、アーカイブの生成をイネーブルにする必要があります。

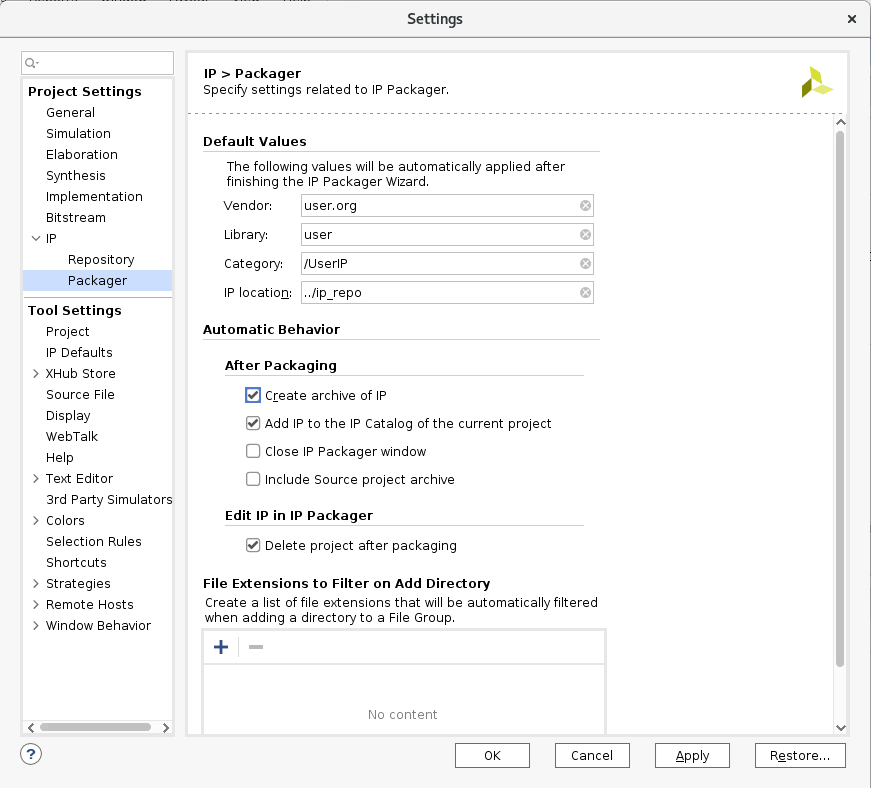

[Review and Package] ページで、[Edit packaging settings] をクリックします。[Settings] ダイアログ ボックスの [IP] → [Package] ページが表示されます。

[After Packaging] セクションで [Create archive of IP] をオンにし、[OK] をクリックします。

[Review and Package] ページがアップデートされ、アーカイブが作成されることが示されます。

[Package IP] をクリックします。

package_xo を使用したカーネルの作成¶

Vivado IP をパッケージしたので、package_xo コマンドを実行して Vitis カーネル (.xo) ファイルを作成できます。package_xo コマンドは、IP ファイルと kernel.xml ファイルを生成された .xo ファイルにパッケージします。

[Tcl Console] ウィンドウに次のコマンドを入力します。

package_xo -force -xo_path <tutorial_path>/reference-files/rtl_kernel/rtl_kernel.srcs/sources_1/imports/Vadd_A_B.xo -kernel_name Vadd_A_B -ip_directory <tutorial_path>/reference-files/rtl_kernel/rtl_kernel.srcs/sources_1/imports/IP

説明:

package_xo: Vivado IP からコンパイル済みオブジェクト ファイル (.xo) を作成するコマンド。

-force: 同じ名前のカーネル ファイルが存在する場合に上書きします。

-xo_path: XO ファイルのパスと名前を指定します。

-kernel_name: 作成するカーネルの名前を指定します。RTL モジュール名と一致している必要があります。

-ip_directory: パッケージ済み Vivado IP を検索するパスを指定します。

ヒント:

package_xoで -kernel_xmlオプションを使用すると、必要に応じて既存のkernel.xmlファイルを指定できます。package_xo コマンドが完了したら、

reference-files/rtl_kernel/rtl_kernel.srcs/sources_1/importsフォルダーに移動してVadd_A_B.xoファイルを確認します。このファイルは、このチュートリアルの後の演習で説明するように、Vitis アプリケーション アクセラレーション フローで使用できます。

次の手順¶

次の手順では、RTL Kernel ウィザード フローを使用します。このウィザードは先ほど作成した Vitis カーネル (.xo) ファイルを再作成しますが、別の方法を使用します。

Copyright© 2020 Xilinx