Overview

The Counter (CTR) mode is a typical block cipher mode of operation using block cipher algorithm.

In this version, we provide Advanced Encryption Standard (AES) processing ability,

the cipherkey length for AES should be 128/192/256 bits.

Another limitation is that our working mode works on units of a fixed size (128 bits for 1 block),

but text in the real world has a variety of lengths.

So, the last block of the text provided to this primitive must be padded to 128 bits before encryption or decryption.

Implementation on FPGA

We support CTR-AES128, CTR-AES192, and CTR-AES256 modes in this implementation.

Attention

The bit-width of the interfaces we provide is shown as follows:

| |

plaintext |

ciphertext |

cipherkey |

IV |

| CTR-AES128 |

128 |

128 |

128 |

128 |

| CTR-AES192 |

128 |

128 |

192 |

128 |

| CTR-AES256 |

128 |

128 |

256 |

128 |

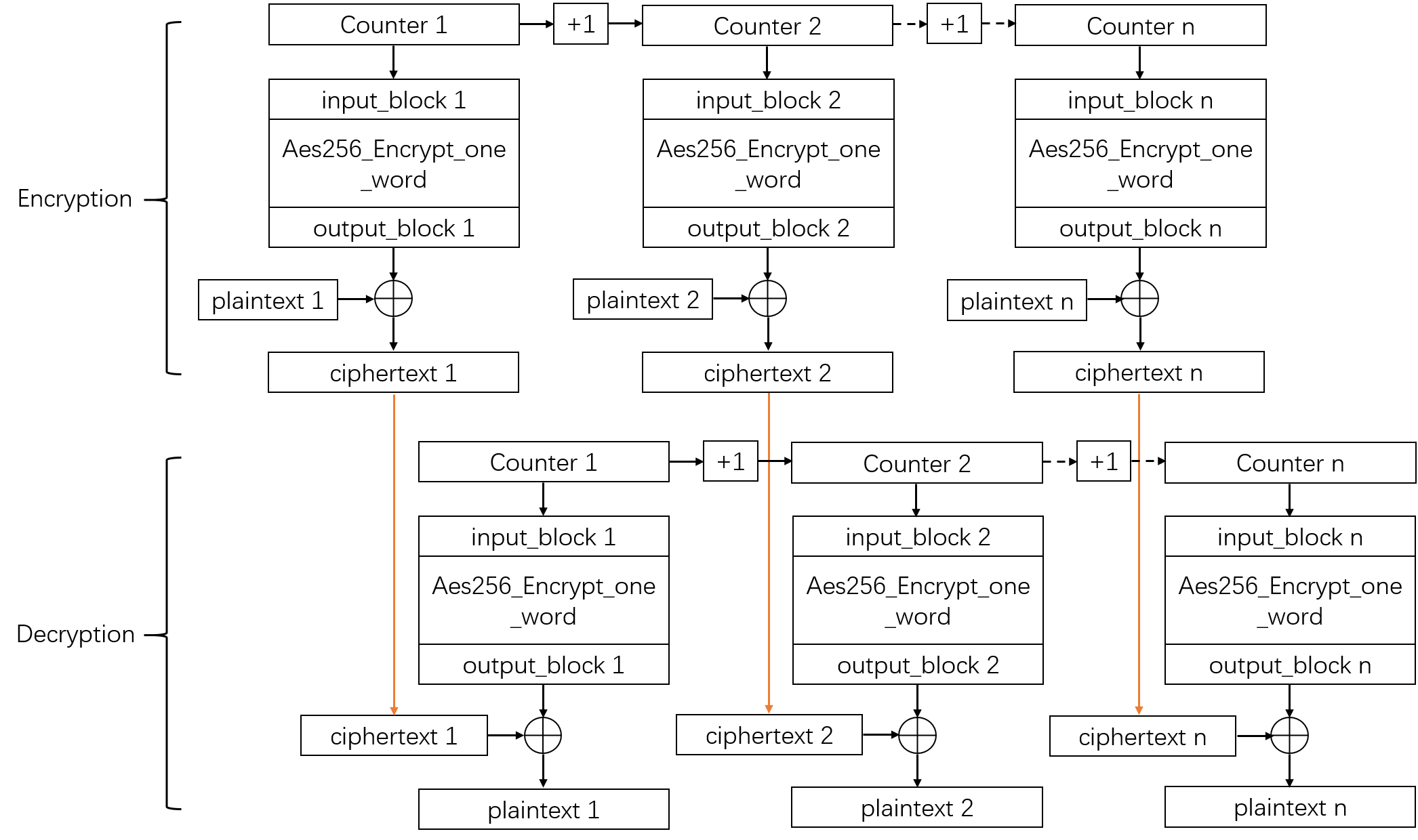

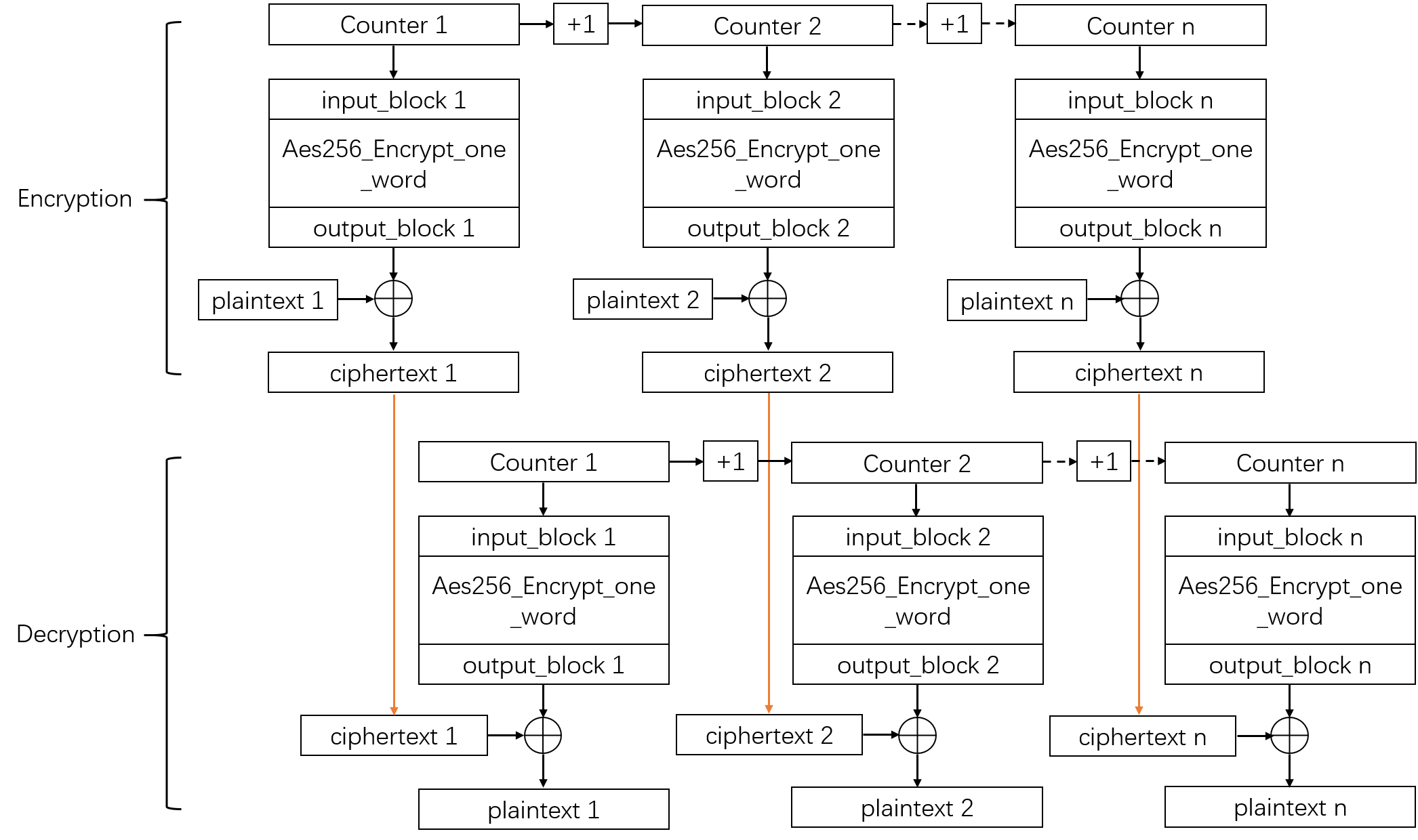

The algorithm flow chart is shown as follow:

As we can see from the chart, both encryption and decryption part of CTR mode has no dependencies,

so the input block of each iteration can be directly calculated by the counter.

Thus, both encryption and decryption part of CTR mode can achieve an initiation interval (II) = 1.