Internals of streamSplit¶

The streamSplit is designed for splitting a wide stream into multiple narrow ones, as it is common to combine several data elements of the same type as a vector and pass them together in FPGA data paths.

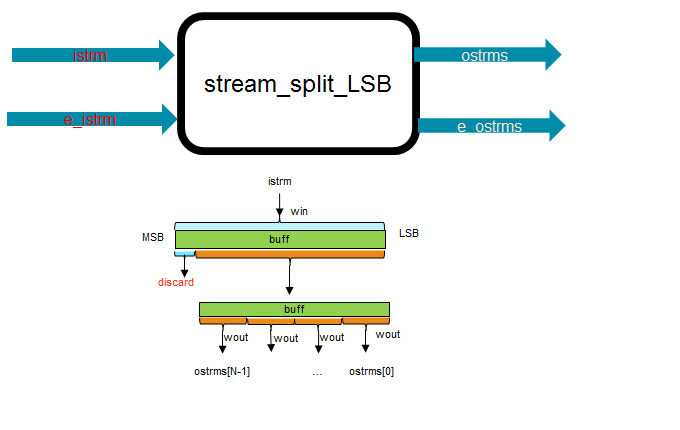

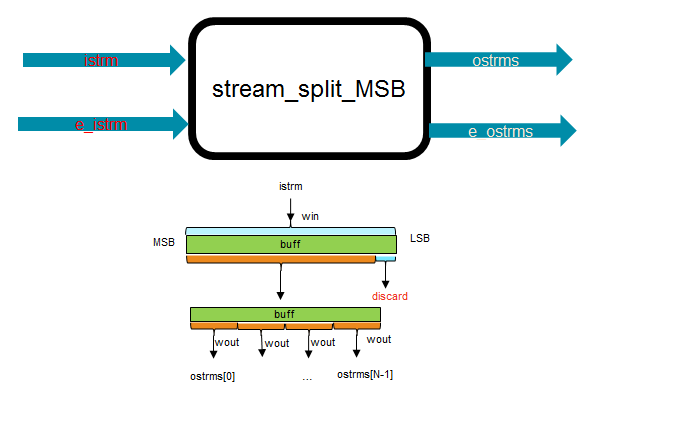

This module offers two static configurations: using the data from LSB or MSB. With LSB option, the element at LSB is sent to output stream with 0 index, while with MSB option, the element at MSB is sent to output with 0 index.

As some storage structures in FPGA are bounded to fixed width or width of power of two, paddings may be necessary sometimes in the combined vector. These padding bits are discarded during splitting, as illustrated below:

Internally, this module is implemented with a simple loop which iteration interval (II) is equal to 1. This means that in each cycle, a vector is split into a set of elements.

Attention

This module expects the width of input stream to be no less than total of output streams. To perform distribution from a vectors of elements to multiple streams, use the streamOneToN module.