#include "aie/Dialect/AIE/IR/AIETargetModel.h"

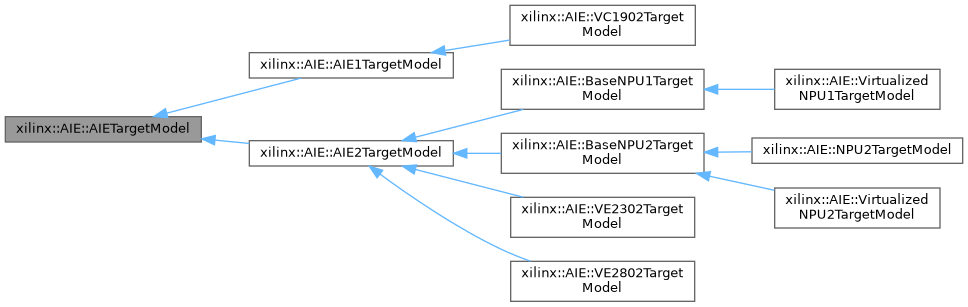

Inheritance diagram for xilinx::AIE::AIETargetModel:

Inheritance diagram for xilinx::AIE::AIETargetModel:Public Types | |

| enum | TargetModelKind { TK_AIE1_VC1902 , TK_AIE1_Last , TK_AIE2_VE2302 , TK_AIE2_VE2802 , TK_AIE2_NPU1_1Col , TK_AIE2_NPU1_2Col , TK_AIE2_NPU1_3Col , TK_AIE2_NPU1_4Col , TK_AIE2_NPU1_Last , TK_AIE2_NPU2 = TK_AIE2_NPU1_Last , TK_AIE2_NPU2_1Col , TK_AIE2_NPU2_2Col , TK_AIE2_NPU2_3Col , TK_AIE2_NPU2_4Col , TK_AIE2_NPU2_5Col , TK_AIE2_NPU2_6Col , TK_AIE2_NPU2_7Col , TK_AIE2_NPU2_Last , TK_AIE2_Last = TK_AIE2_NPU2_Last } |

| enum | ModelProperty { UsesSemaphoreLocks = 1U << 0 , IsNPU = 1U << 1 , IsVirtualized = 1U << 2 , UsesMultiDimensionalBDs = 1U << 3 } |

Public Member Functions | |

| TargetModelKind | getKind () const |

| AIETargetModel (TargetModelKind k) | |

| virtual | ~AIETargetModel () |

| virtual AIEArch | getTargetArch () const =0 |

| Return the target architecture. | |

| virtual uint32_t | getAddressGenGranularity () const =0 |

| Return the data bus width of the device. | |

| virtual int | columns () const =0 |

| Return the number of columns in the device. | |

| virtual int | rows () const =0 |

| Return the number of rows in the device. | |

| virtual AIETileType | getTileType (int col, int row) const =0 |

| Return the tile type for the given tile coordinates. | |

| bool | isCoreTile (int col, int row) const |

| Return true if the given tile is a Core tile. | |

| bool | isMemTile (int col, int row) const |

| Return true if the given tile is a Mem tile. | |

| bool | isShimNOCTile (int col, int row) const |

| Return true if the given tile is a ShimNOC tile. | |

| bool | isShimPLTile (int col, int row) const |

| Return true if the given tile is a ShimPL tile. | |

| bool | isShimNOCorPLTile (int col, int row) const |

| Return true if the given tile is either a ShimNOC or ShimPL tile. | |

| virtual bool | isValidTile (TileID src) const |

| Return true if the given tile ID is valid. | |

| virtual std::optional< TileID > | getMemWest (TileID src) const =0 |

| Return the tile ID of the memory to the west of the given tile, if it exists. | |

| virtual std::optional< TileID > | getMemEast (TileID src) const =0 |

| Return the tile ID of the memory to the east of the given tile, if it exists. | |

| virtual std::optional< TileID > | getMemNorth (TileID src) const =0 |

| Return the tile ID of the memory to the north of the given tile, if it exists. | |

| virtual std::optional< TileID > | getMemSouth (TileID src) const =0 |

| Return the tile ID of the memory to the south of the given tile, if it exists. | |

| bool | isInternal (int srcCol, int srcRow, int dstCol, int dstRow) const |

| Return true if src is the internal memory of dst. | |

| bool | isWest (int srcCol, int srcRow, int dstCol, int dstRow) const |

| Return true if src is West of dst. | |

| bool | isEast (int srcCol, int srcRow, int dstCol, int dstRow) const |

| Return true if src is East of dst. | |

| bool | isNorth (int srcCol, int srcRow, int dstCol, int dstRow) const |

| Return true if src is North of dst. | |

| bool | isSouth (int srcCol, int srcRow, int dstCol, int dstRow) const |

| Return true if src is South of dst. | |

| virtual bool | isMemWest (int srcCol, int srcRow, int dstCol, int dstRow) const =0 |

| Return true if src has a memory tile which is West of dst. | |

| virtual bool | isMemEast (int srcCol, int srcRow, int dstCol, int dstRow) const =0 |

| Return true if src has a memory tile which is East of dst. | |

| virtual bool | isMemNorth (int srcCol, int srcRow, int dstCol, int dstRow) const =0 |

| Return true if src has a memory tile which is North of dst. | |

| virtual bool | isMemSouth (int srcCol, int srcRow, int dstCol, int dstRow) const =0 |

| Return true if src has a memory tile which is South of dst. | |

| virtual bool | isLegalMemAffinity (int coreCol, int coreRow, int memCol, int memRow) const =0 |

| Return true if core can access the memory in mem. | |

| virtual uint32_t | getMemInternalBaseAddress (TileID src) const =0 |

| Return the base address in the local address map for a core. | |

| virtual uint32_t | getMemSouthBaseAddress () const =0 |

| Return the base address in the local address map for a core. | |

| virtual uint32_t | getMemWestBaseAddress () const =0 |

| Return the base address in the local address map for a core. | |

| virtual uint32_t | getMemNorthBaseAddress () const =0 |

| Return the base address in the local address map for a core. | |

| virtual uint32_t | getMemEastBaseAddress () const =0 |

| Return the base address in the local address map for a core. | |

| std::optional< uint32_t > | getLockLocalBaseIndex (int localCol, int localRow, int lockCol, int lockRow) const |

| Return the lock base index (or offset) in the local tile when accessing a neighbor's lock or an empty optional if an invalid neighbor is given Takes into account differences between Memory and Core tiles. | |

| std::optional< uint32_t > | getMemLocalBaseAddress (int localCol, int localRow, int memCol, int memRow) const |

| Return the memory base address (or offset) in the local tile when accessing a neighbor's memory or an empty optional if an invalid neighbor is given Takes into account differences between Memory and Core tiles. | |

| virtual uint32_t | getLocalMemorySize () const =0 |

| Return the size (in bytes) of the local data memory of a core. | |

| virtual uint32_t | getAccumulatorCascadeSize () const =0 |

| Return the size (in bits) of the accumulator/cascade. | |

| virtual uint32_t | getNumLocks (AIETileType tileType) const =0 |

| Return the number of lock objects for a given tile type. | |

| uint32_t | getNumLocks (int col, int row) const |

| Return the number of lock objects for a tile at the given coordinates. | |

| virtual uint32_t | getMaxLockValue () const =0 |

| Return the maximum value that can be stored in a lock register. | |

| virtual std::optional< uint32_t > | getLocalLockAddress (uint32_t lockId, TileID tile) const =0 |

| virtual uint32_t | getNumBDs (AIETileType tileType) const =0 |

| Return the number of buffer descriptors for a given tile type. | |

| virtual std::optional< uint32_t > | getStreamSwitchPortIndex (int col, int row, WireBundle bundle, uint32_t channel, bool master) const =0 |

| Get stream switch port index for a given port specification Return port index for Stream_Switch_Event_Port_Selection register, or nullopt if invalid. | |

| uint32_t | getNumBDs (int col, int row) const |

| Return the number of buffer descriptors supported by the DMA in the given tile. | |

| uint32_t | getNumBDsForChannel (int col, int row, int channel) const |

Return the number of buffer descriptors accessible on channel channel for the tile at (col, row). | |

| virtual bool | isBdChannelAccessible (int col, int row, uint32_t bd_id, int channel) const =0 |

Return true iff buffer descriptor bd_id on tile (col, row) can be submitted on channel channel. | |

| virtual uint64_t | getDmaBdAddress (int col, int row, uint32_t bd_id, int channel=-1, AIE::DMAChannelDir direction=AIE::DMAChannelDir::MM2S) const =0 |

| Return the array address of the dma buffer descriptor for the given col, row, buffer descriptor id, channel and direction. | |

| virtual uint32_t | getDmaBdAddressOffset (int col, int row) const =0 |

| Return the offset of the base address field within the shim dma buffer descriptor. | |

| virtual uint32_t | getDmaControlAddress (int col, int row, int channel, AIE::DMAChannelDir direction) const =0 |

| Return the array address of the dma task queue register for the given col, row, channel and direction. | |

| virtual uint32_t | getNumMemTileRows () const =0 |

| virtual uint32_t | getMemTileSize () const =0 |

| Return the size (in bytes) of a MemTile. | |

| virtual uint32_t | getNumBanks (int col, int row) const =0 |

| Return the number of memory banks of a given tile. | |

| virtual uint32_t | getMaxChannelNumForAdjacentMemTile (int col, int row) const =0 |

| virtual uint32_t | getNumDestSwitchboxConnections (int col, int row, WireBundle bundle) const =0 |

| Return the number of destinations of connections inside a switchbox. | |

| virtual uint32_t | getNumSourceSwitchboxConnections (int col, int row, WireBundle bundle) const =0 |

| Return the number of sources of connections inside a switchbox. | |

| virtual uint32_t | getNumDestShimMuxConnections (int col, int row, WireBundle bundle) const =0 |

| Return the number of destinations of connections inside a shimmux. | |

| virtual uint32_t | getNumSourceShimMuxConnections (int col, int row, WireBundle bundle) const =0 |

| Return the number of sources of connections inside a shimmux. | |

| virtual bool | isLegalTileConnection (int col, int row, WireBundle srcBundle, int srcChan, WireBundle dstBundle, int dstChan) const =0 |

| void | validate () const |

| uint32_t | getModelProperties () const |

| void | addModelProperty (uint32_t prop) |

| bool | hasProperty (ModelProperty Prop) const |

| virtual uint32_t | getColumnShift () const =0 |

| virtual uint32_t | getRowShift () const =0 |

| virtual std::vector< std::pair< uint32_t, uint32_t > > | getShimBurstEncodingsAndLengths () const =0 |

| virtual bool | isSupportedBlockFormat (std::string const &format) const |

| const RegisterInfo * | lookupRegister (llvm::StringRef name, TileID tile, bool isMem=false) const |

| Register Database API - provides access to register and event information for trace configuration and low-level register access. | |

| std::optional< uint32_t > | lookupEvent (llvm::StringRef name, TileID tile, bool isMem=false) const |

| Lookup event number by name and tile. | |

| uint32_t | encodeFieldValue (const BitFieldInfo &field, uint32_t value) const |

| Encode a field value with proper bit shifting. | |

| std::optional< uint32_t > | getFieldMask (const BitFieldInfo &field) const |

| Compute a 32-bit mask for a register field. | |

| std::optional< uint32_t > | resolvePortValue (llvm::StringRef value, TileID tile, bool master) const |

| Resolve stream switch port specification to port index. | |

Protected Member Functions | |

| virtual std::unique_ptr< RegisterDatabase > | loadRegisterDatabase () const |

| Subclasses override to provide architecture-specific database loading. | |

| const RegisterDatabase * | getRegisterDatabase () const |

| Get the register database, loading it lazily on first access. | |

Detailed Description

Definition at line 58 of file AIETargetModel.h.

Member Enumeration Documentation

◆ ModelProperty

| Enumerator | |

|---|---|

| UsesSemaphoreLocks | |

| IsNPU | |

| IsVirtualized | |

| UsesMultiDimensionalBDs | |

Definition at line 85 of file AIETargetModel.h.

◆ TargetModelKind

Definition at line 61 of file AIETargetModel.h.

Constructor & Destructor Documentation

◆ AIETargetModel()

|

inline |

Definition at line 121 of file AIETargetModel.h.

◆ ~AIETargetModel()

|

virtualdefault |

Member Function Documentation

◆ addModelProperty()

|

inline |

Definition at line 364 of file AIETargetModel.h.

Referenced by xilinx::AIE::AIE2TargetModel::AIE2TargetModel(), xilinx::AIE::BaseNPU1TargetModel::BaseNPU1TargetModel(), xilinx::AIE::BaseNPU2TargetModel::BaseNPU2TargetModel(), xilinx::AIE::VirtualizedNPU1TargetModel::VirtualizedNPU1TargetModel(), and xilinx::AIE::VirtualizedNPU2TargetModel::VirtualizedNPU2TargetModel().

◆ columns()

|

pure virtual |

Return the number of columns in the device.

Implemented in xilinx::AIE::VC1902TargetModel, xilinx::AIE::VE2302TargetModel, xilinx::AIE::VE2802TargetModel, xilinx::AIE::VirtualizedNPU1TargetModel, xilinx::AIE::NPU2TargetModel, and xilinx::AIE::VirtualizedNPU2TargetModel.

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), aieTargetModelColumns(), xilinx::AIE::AIE1TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE1TargetModel::getNumSourceSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceSwitchboxConnections(), getRowToShimChanMap(), getTileToControllerIdMap(), getTileToControllerIdMap6RowsOrLess(), xilinx::AIE::SequentialPlacer::initialize(), isValidTile(), and validate().

◆ encodeFieldValue()

| uint32_t xilinx::AIE::AIETargetModel::encodeFieldValue | ( | const BitFieldInfo & | field, |

| uint32_t | value | ||

| ) | const |

Encode a field value with proper bit shifting.

Return Value shifted to correct bit position

Definition at line 79 of file AIETargetModel.cpp.

References getRegisterDatabase().

◆ getAccumulatorCascadeSize()

|

pure virtual |

Return the size (in bits) of the accumulator/cascade.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getAddressGenGranularity()

|

pure virtual |

Return the data bus width of the device.

Implemented in xilinx::AIE::AIE2TargetModel, and xilinx::AIE::VC1902TargetModel.

Referenced by aieGetTargetModelAddressGenGranularity(), and xilinx::AIEX::getHardwareStridesWraps().

◆ getColumnShift()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), and aieTargetModelGetColumnShift().

◆ getDmaBdAddress()

|

pure virtual |

Return the array address of the dma buffer descriptor for the given col, row, buffer descriptor id, channel and direction.

Not all architecture variants will use channel and direction so these have default values.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by AIEDMATasksToNPUPass::setAddressForSingleBD().

◆ getDmaBdAddressOffset()

|

pure virtual |

Return the offset of the base address field within the shim dma buffer descriptor.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by AIEDMATasksToNPUPass::setAddressForSingleBD().

◆ getDmaControlAddress()

|

pure virtual |

Return the array address of the dma task queue register for the given col, row, channel and direction.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getFieldMask()

| std::optional< uint32_t > xilinx::AIE::AIETargetModel::getFieldMask | ( | const BitFieldInfo & | field | ) | const |

Compute a 32-bit mask for a register field.

Return nullopt if the field does not fit in a 32-bit register.

Definition at line 88 of file AIETargetModel.cpp.

References xilinx::AIE::BitFieldInfo::bit_end, xilinx::AIE::BitFieldInfo::bit_start, and xilinx::AIE::BitFieldInfo::getWidth().

◆ getKind()

|

inline |

Definition at line 119 of file AIETargetModel.h.

Referenced by xilinx::AIE::AIE1TargetModel::classof(), xilinx::AIE::AIE2TargetModel::classof(), xilinx::AIE::VC1902TargetModel::classof(), xilinx::AIE::VE2302TargetModel::classof(), xilinx::AIE::VE2802TargetModel::classof(), xilinx::AIE::BaseNPU1TargetModel::classof(), xilinx::AIE::VirtualizedNPU1TargetModel::classof(), xilinx::AIE::BaseNPU2TargetModel::classof(), xilinx::AIE::NPU2TargetModel::classof(), and xilinx::AIE::VirtualizedNPU2TargetModel::classof().

◆ getLocalLockAddress()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getLocalMemorySize()

|

pure virtual |

Return the size (in bytes) of the local data memory of a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetLocalMemorySize().

◆ getLockLocalBaseIndex()

| std::optional< uint32_t > xilinx::AIE::AIETargetModel::getLockLocalBaseIndex | ( | int | localCol, |

| int | localRow, | ||

| int | lockCol, | ||

| int | lockRow | ||

| ) | const |

Return the lock base index (or offset) in the local tile when accessing a neighbor's lock or an empty optional if an invalid neighbor is given Takes into account differences between Memory and Core tiles.

Definition at line 1504 of file AIETargetModel.cpp.

References getNumLocks(), isCoreTile(), isEast(), isInternal(), isMemEast(), isMemNorth(), isMemSouth(), isMemTile(), isMemWest(), and isWest().

Referenced by configureLocksInBdBlock().

◆ getMaxChannelNumForAdjacentMemTile()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMaxChannelNumForAdjacentMemTile().

◆ getMaxLockValue()

|

pure virtual |

Return the maximum value that can be stored in a lock register.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemEast()

|

pure virtual |

Return the tile ID of the memory to the east of the given tile, if it exists.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemEastBaseAddress()

|

pure virtual |

Return the base address in the local address map for a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMemEastBaseAddress(), and getMemLocalBaseAddress().

◆ getMemInternalBaseAddress()

|

pure virtual |

Return the base address in the local address map for a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemLocalBaseAddress()

| std::optional< uint32_t > xilinx::AIE::AIETargetModel::getMemLocalBaseAddress | ( | int | localCol, |

| int | localRow, | ||

| int | memCol, | ||

| int | memRow | ||

| ) | const |

Return the memory base address (or offset) in the local tile when accessing a neighbor's memory or an empty optional if an invalid neighbor is given Takes into account differences between Memory and Core tiles.

Definition at line 1530 of file AIETargetModel.cpp.

References getMemEastBaseAddress(), getMemNorthBaseAddress(), getMemSouthBaseAddress(), getMemTileSize(), getMemWestBaseAddress(), isCoreTile(), isEast(), isInternal(), isMemEast(), isMemNorth(), isMemSouth(), isMemTile(), isMemWest(), and isWest().

Referenced by configureBdInBlock(), and AIEDMATasksToNPUPass::setAddressForSingleBD().

◆ getMemNorth()

|

pure virtual |

Return the tile ID of the memory to the north of the given tile, if it exists.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemNorthBaseAddress()

|

pure virtual |

Return the base address in the local address map for a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMemNorthBaseAddress(), and getMemLocalBaseAddress().

◆ getMemSouth()

|

pure virtual |

Return the tile ID of the memory to the south of the given tile, if it exists.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemSouthBaseAddress()

|

pure virtual |

Return the base address in the local address map for a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMemSouthBaseAddress(), and getMemLocalBaseAddress().

◆ getMemTileSize()

|

pure virtual |

Return the size (in bytes) of a MemTile.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMemTileSize(), and getMemLocalBaseAddress().

◆ getMemWest()

|

pure virtual |

Return the tile ID of the memory to the west of the given tile, if it exists.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

◆ getMemWestBaseAddress()

|

pure virtual |

Return the base address in the local address map for a core.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetMemWestBaseAddress(), and getMemLocalBaseAddress().

◆ getModelProperties()

|

inline |

Definition at line 363 of file AIETargetModel.h.

Referenced by hasProperty().

◆ getNumBanks()

|

pure virtual |

Return the number of memory banks of a given tile.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumBanks().

◆ getNumBDs() [1/2]

|

pure virtual |

Return the number of buffer descriptors for a given tile type.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumBDs(), getNumBDs(), getNumBDsForChannel(), and BdIdGenerator::nextBdId().

◆ getNumBDs() [2/2]

|

inline |

Return the number of buffer descriptors supported by the DMA in the given tile.

Definition at line 291 of file AIETargetModel.h.

References xilinx::AIE::col, getNumBDs(), getTileType(), and xilinx::AIE::row.

◆ getNumBDsForChannel()

|

inline |

Return the number of buffer descriptors accessible on channel channel for the tile at (col, row).

For tiles with no per-channel BD partitioning this equals getNumBDs(col, row).

Definition at line 298 of file AIETargetModel.h.

References xilinx::AIE::channel, xilinx::AIE::col, getNumBDs(), isBdChannelAccessible(), and xilinx::AIE::row.

Referenced by AIEAssignBufferDescriptorIDsPass::runOnOperation().

◆ getNumDestShimMuxConnections()

|

pure virtual |

Return the number of destinations of connections inside a shimmux.

These are the targets of connect operations in the switchbox.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumDestShimMuxConnections(), and xilinx::AIE::Pathfinder::initialize().

◆ getNumDestSwitchboxConnections()

|

pure virtual |

Return the number of destinations of connections inside a switchbox.

These are the targets of connect operations in the switchbox.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumDestSwitchboxConnections(), xilinx::AIE::Pathfinder::initialize(), and validate().

◆ getNumLocks() [1/2]

|

pure virtual |

Return the number of lock objects for a given tile type.

Implemented in xilinx::AIE::AIE1TargetModel, xilinx::AIE::AIE2TargetModel, xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumLocks(), getLockLocalBaseIndex(), and getNumLocks().

◆ getNumLocks() [2/2]

|

inline |

Return the number of lock objects for a tile at the given coordinates.

Definition at line 267 of file AIETargetModel.h.

References xilinx::AIE::col, getNumLocks(), getTileType(), and xilinx::AIE::row.

◆ getNumMemTileRows()

|

pure virtual |

◆ getNumSourceShimMuxConnections()

|

pure virtual |

Return the number of sources of connections inside a shimmux.

These are the origins of connect operations in the switchbox.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumSourceShimMuxConnections(), getRowToShimChanMap(), and xilinx::AIE::Pathfinder::initialize().

◆ getNumSourceSwitchboxConnections()

|

pure virtual |

Return the number of sources of connections inside a switchbox.

These are the origins of connect operations in the switchbox.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelGetNumSourceSwitchboxConnections(), xilinx::AIE::Pathfinder::initialize(), and validate().

◆ getRegisterDatabase()

|

protected |

Get the register database, loading it lazily on first access.

Throws fatal error if database is required but unavailable.

Definition at line 56 of file AIETargetModel.cpp.

References loadRegisterDatabase().

Referenced by encodeFieldValue(), lookupEvent(), and lookupRegister().

◆ getRowShift()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), and aieTargetModelGetRowShift().

◆ getShimBurstEncodingsAndLengths()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, xilinx::AIE::AIE2TargetModel, and xilinx::AIE::BaseNPU2TargetModel.

◆ getStreamSwitchPortIndex()

|

pure virtual |

Get stream switch port index for a given port specification Return port index for Stream_Switch_Event_Port_Selection register, or nullopt if invalid.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by resolvePortValue().

◆ getTargetArch()

|

pure virtual |

Return the target architecture.

Implemented in xilinx::AIE::AIE1TargetModel, xilinx::AIE::AIE2TargetModel, and xilinx::AIE::BaseNPU2TargetModel.

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), and AIEDMATasksToNPUPass::setAddressForSingleBD().

◆ getTileType()

|

pure virtual |

Return the tile type for the given tile coordinates.

- CoreTile: tiles with a Core, TileDMA, tile memory, and stream connections.

- MemTile: tiles with TileDMA, tile memory, and stream connections, but no core.

- ShimNOCTile: tiles with ShimDMA and connection to the memory-mapped NOC.

- ShimPLTile: tiles with connections to the PL, no ShimDMA.

Implemented in xilinx::AIE::VC1902TargetModel, xilinx::AIE::VE2302TargetModel, xilinx::AIE::VE2802TargetModel, xilinx::AIE::VirtualizedNPU1TargetModel, and xilinx::AIE::BaseNPU2TargetModel.

Referenced by xilinx::AIE::AIE2TargetModel::getNumBanks(), getNumBDs(), getNumLocks(), xilinx::AIE::SequentialPlacer::initialize(), xilinx::AIE::AIE2TargetModel::isBdChannelAccessible(), isCoreTile(), isMemTile(), isShimNOCorPLTile(), isShimNOCTile(), and isShimPLTile().

◆ hasProperty()

|

inline |

Definition at line 366 of file AIETargetModel.h.

References getModelProperties().

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), and aieTargetModelIsNPU().

◆ isBdChannelAccessible()

|

pure virtual |

Return true iff buffer descriptor bd_id on tile (col, row) can be submitted on channel channel.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by getNumBDsForChannel(), and BdIdGenerator::nextBdId().

◆ isCoreTile()

|

inline |

Return true if the given tile is a Core tile.

Definition at line 147 of file AIETargetModel.h.

References xilinx::AIE::col, getTileType(), and xilinx::AIE::row.

Referenced by aieTargetModelIsCoreTile(), xilinx::AIE::AIE1TargetModel::getDmaBdAddress(), xilinx::AIE::AIE2TargetModel::getDmaBdAddress(), xilinx::AIE::AIE1TargetModel::getDmaBdAddressOffset(), xilinx::AIE::AIE2TargetModel::getDmaBdAddressOffset(), xilinx::AIE::AIE1TargetModel::getDmaControlAddress(), xilinx::AIE::AIE2TargetModel::getDmaControlAddress(), xilinx::AIE::AIE2TargetModel::getLocalLockAddress(), getLockLocalBaseIndex(), getMemLocalBaseAddress(), xilinx::AIE::AIE1TargetModel::getStreamSwitchPortIndex(), xilinx::AIE::AIE2TargetModel::getStreamSwitchPortIndex(), xilinx::AIE::AIE1TargetModel::isLegalTileConnection(), xilinx::AIE::AIE2TargetModel::isLegalTileConnection(), AIEDMATasksToNPUPass::setAddressForSingleBD(), and validate().

◆ isEast()

|

inline |

Return true if src is East of dst.

Definition at line 202 of file AIETargetModel.h.

Referenced by aieTargetModelIsEast(), getLockLocalBaseIndex(), getMemLocalBaseAddress(), xilinx::AIE::AIE1TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE2TargetModel::isLegalMemAffinity(), and xilinx::AIE::AIE1TargetModel::isMemEast().

◆ isInternal()

|

inline |

Return true if src is the internal memory of dst.

Definition at line 192 of file AIETargetModel.h.

Referenced by aieTargetModelIsInternal(), getLockLocalBaseIndex(), getMemLocalBaseAddress(), xilinx::AIE::AIE1TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE2TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE1TargetModel::isMemEast(), xilinx::AIE::AIE2TargetModel::isMemEast(), and xilinx::AIE::AIE1TargetModel::isMemWest().

◆ isLegalMemAffinity()

|

pure virtual |

Return true if core can access the memory in mem.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelIsLegalMemAffinity().

◆ isLegalTileConnection()

|

pure virtual |

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by xilinx::AIE::Pathfinder::initialize(), isLegalTileConnection(), and isLegalTileConnection().

◆ isMemEast()

|

pure virtual |

Return true if src has a memory tile which is East of dst.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelIsMemEast(), getLockLocalBaseIndex(), and getMemLocalBaseAddress().

◆ isMemNorth()

|

pure virtual |

Return true if src has a memory tile which is North of dst.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelIsMemNorth(), getLockLocalBaseIndex(), and getMemLocalBaseAddress().

◆ isMemSouth()

|

pure virtual |

Return true if src has a memory tile which is South of dst.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelIsMemSouth(), getLockLocalBaseIndex(), and getMemLocalBaseAddress().

◆ isMemTile()

|

inline |

Return true if the given tile is a Mem tile.

Definition at line 152 of file AIETargetModel.h.

References xilinx::AIE::col, getTileType(), and xilinx::AIE::row.

Referenced by aieTargetModelIsMemTile(), configureBdInBlock(), configureLocksInBdBlock(), xilinx::AIE::AIE2TargetModel::getDmaBdAddress(), xilinx::AIE::AIE2TargetModel::getDmaControlAddress(), xilinx::AIE::AIE2TargetModel::getLocalLockAddress(), getLockLocalBaseIndex(), getMemLocalBaseAddress(), xilinx::AIE::AIE2TargetModel::getMemSouth(), xilinx::AIE::AIE2TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getStreamSwitchPortIndex(), xilinx::AIE::AIE2TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE1TargetModel::isLegalTileConnection(), xilinx::AIE::AIE2TargetModel::isLegalTileConnection(), AIEDMATasksToNPUPass::setAddressForSingleBD(), and validate().

◆ isMemWest()

|

pure virtual |

Return true if src has a memory tile which is West of dst.

Implemented in xilinx::AIE::AIE1TargetModel, and xilinx::AIE::AIE2TargetModel.

Referenced by aieTargetModelIsMemWest(), getLockLocalBaseIndex(), and getMemLocalBaseAddress().

◆ isNorth()

|

inline |

Return true if src is North of dst.

Definition at line 207 of file AIETargetModel.h.

Referenced by aieTargetModelIsNorth(), xilinx::AIE::AIE1TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE1TargetModel::isMemNorth(), and xilinx::AIE::AIE2TargetModel::isMemNorth().

◆ isShimNOCorPLTile()

|

inline |

Return true if the given tile is either a ShimNOC or ShimPL tile.

Definition at line 167 of file AIETargetModel.h.

References xilinx::AIE::col, getTileType(), and xilinx::AIE::row.

Referenced by aieTargetModelIsShimNOCorPLTile(), xilinx::AIE::AIE2TargetModel::getLocalLockAddress(), xilinx::AIE::AIE1TargetModel::getNumDestShimMuxConnections(), xilinx::AIE::AIE2TargetModel::getNumDestShimMuxConnections(), xilinx::AIE::AIE1TargetModel::getNumSourceShimMuxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceShimMuxConnections(), xilinx::AIE::AIE1TargetModel::getStreamSwitchPortIndex(), xilinx::AIE::Pathfinder::initialize(), xilinx::AIE::AIE1TargetModel::isLegalTileConnection(), and xilinx::AIE::AIE2TargetModel::isLegalTileConnection().

◆ isShimNOCTile()

|

inline |

Return true if the given tile is a ShimNOC tile.

Definition at line 157 of file AIETargetModel.h.

References xilinx::AIE::col, getTileType(), and xilinx::AIE::row.

Referenced by aieTargetModelIsShimNOCTile(), configureBdInBlock(), xilinx::AIE::AIE1TargetModel::getDmaBdAddress(), xilinx::AIE::AIE2TargetModel::getDmaBdAddress(), xilinx::AIE::AIE1TargetModel::getDmaBdAddressOffset(), xilinx::AIE::AIE1TargetModel::getDmaControlAddress(), xilinx::AIE::AIE2TargetModel::getDmaControlAddress(), xilinx::AIE::AIE1TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE1TargetModel::getNumSourceSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceSwitchboxConnections(), getRowToShimChanMap(), xilinx::AIE::AIE2TargetModel::getStreamSwitchPortIndex(), AIEDMATasksToNPUPass::setAddressForSingleBD(), and validate().

◆ isShimPLTile()

|

inline |

Return true if the given tile is a ShimPL tile.

Definition at line 162 of file AIETargetModel.h.

References xilinx::AIE::col, getTileType(), and xilinx::AIE::row.

Referenced by aieTargetModelIsShimPLTile(), xilinx::AIE::AIE1TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE1TargetModel::getNumSourceSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceSwitchboxConnections(), and validate().

◆ isSouth()

|

inline |

Return true if src is South of dst.

Definition at line 212 of file AIETargetModel.h.

Referenced by aieTargetModelIsSouth(), xilinx::AIE::AIE1TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE1TargetModel::isMemSouth(), and xilinx::AIE::AIE2TargetModel::isMemSouth().

◆ isSupportedBlockFormat()

|

virtual |

Reimplemented in xilinx::AIE::BaseNPU2TargetModel.

Definition at line 1555 of file AIETargetModel.cpp.

Referenced by BfpToIntegerConverter::BfpToIntegerConverter().

◆ isValidTile()

Return true if the given tile ID is valid.

Definition at line 173 of file AIETargetModel.h.

References columns(), rows(), and xilinx::AIE::src.

Referenced by xilinx::AIE::AIE1TargetModel::getMemEast(), xilinx::AIE::AIE2TargetModel::getMemEast(), xilinx::AIE::AIE1TargetModel::getMemNorth(), xilinx::AIE::AIE2TargetModel::getMemNorth(), xilinx::AIE::AIE1TargetModel::getMemSouth(), xilinx::AIE::AIE2TargetModel::getMemSouth(), xilinx::AIE::AIE1TargetModel::getMemWest(), and xilinx::AIE::AIE2TargetModel::getMemWest().

◆ isWest()

|

inline |

Return true if src is West of dst.

Definition at line 197 of file AIETargetModel.h.

Referenced by aieTargetModelIsWest(), getLockLocalBaseIndex(), getMemLocalBaseAddress(), xilinx::AIE::AIE1TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE2TargetModel::isLegalMemAffinity(), xilinx::AIE::AIE1TargetModel::isMemWest(), and xilinx::AIE::AIE2TargetModel::isMemWest().

◆ loadRegisterDatabase()

|

protectedvirtual |

Subclasses override to provide architecture-specific database loading.

Returns nullptr if register database is not available for this architecture.

Reimplemented in xilinx::AIE::AIE2TargetModel.

Definition at line 51 of file AIETargetModel.cpp.

Referenced by getRegisterDatabase().

◆ lookupEvent()

| std::optional< uint32_t > xilinx::AIE::AIETargetModel::lookupEvent | ( | llvm::StringRef | name, |

| TileID | tile, | ||

| bool | isMem = false |

||

| ) | const |

Lookup event number by name and tile.

Return Event number if found, nullopt otherwise

Definition at line 70 of file AIETargetModel.cpp.

References getRegisterDatabase().

◆ lookupRegister()

| const RegisterInfo * xilinx::AIE::AIETargetModel::lookupRegister | ( | llvm::StringRef | name, |

| TileID | tile, | ||

| bool | isMem = false |

||

| ) | const |

Register Database API - provides access to register and event information for trace configuration and low-level register access.

Lookup register information by name and tile. Return pointer to register info, or nullptr if not found

Definition at line 61 of file AIETargetModel.cpp.

References getRegisterDatabase().

◆ resolvePortValue()

| std::optional< uint32_t > xilinx::AIE::AIETargetModel::resolvePortValue | ( | llvm::StringRef | value, |

| TileID | tile, | ||

| bool | master | ||

| ) | const |

Resolve stream switch port specification to port index.

Return Port index for stream switch register, or nullopt if invalid

Definition at line 101 of file AIETargetModel.cpp.

References xilinx::AIE::channel, and getStreamSwitchPortIndex().

◆ rows()

|

pure virtual |

Return the number of rows in the device.

Implemented in xilinx::AIE::VC1902TargetModel, xilinx::AIE::VE2302TargetModel, xilinx::AIE::VE2802TargetModel, xilinx::AIE::BaseNPU1TargetModel, and xilinx::AIE::BaseNPU2TargetModel.

Referenced by xilinx::AIE::AIERTControl::AIERTControl(), aieTargetModelRows(), xilinx::AIE::AIE1TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumDestSwitchboxConnections(), xilinx::AIE::AIE1TargetModel::getNumSourceSwitchboxConnections(), xilinx::AIE::AIE2TargetModel::getNumSourceSwitchboxConnections(), getRowToShimChanMap(), getTileToControllerIdMap(), getTileToControllerIdMap6RowsOrLess(), xilinx::AIE::SequentialPlacer::initialize(), isValidTile(), and validate().

◆ validate()

| void xilinx::AIE::AIETargetModel::validate | ( | ) | const |

Definition at line 1445 of file AIETargetModel.cpp.

References columns(), getNumDestSwitchboxConnections(), getNumMemTileRows(), getNumSourceSwitchboxConnections(), isCoreTile(), isMemTile(), isShimNOCTile(), isShimPLTile(), and rows().

The documentation for this class was generated from the following files:

- include/aie/Dialect/AIE/IR/AIETargetModel.h

- lib/Dialect/AIE/IR/AIETargetModel.cpp