AVED V80/V80P - Clock Reset Module¶

Clock Reset¶

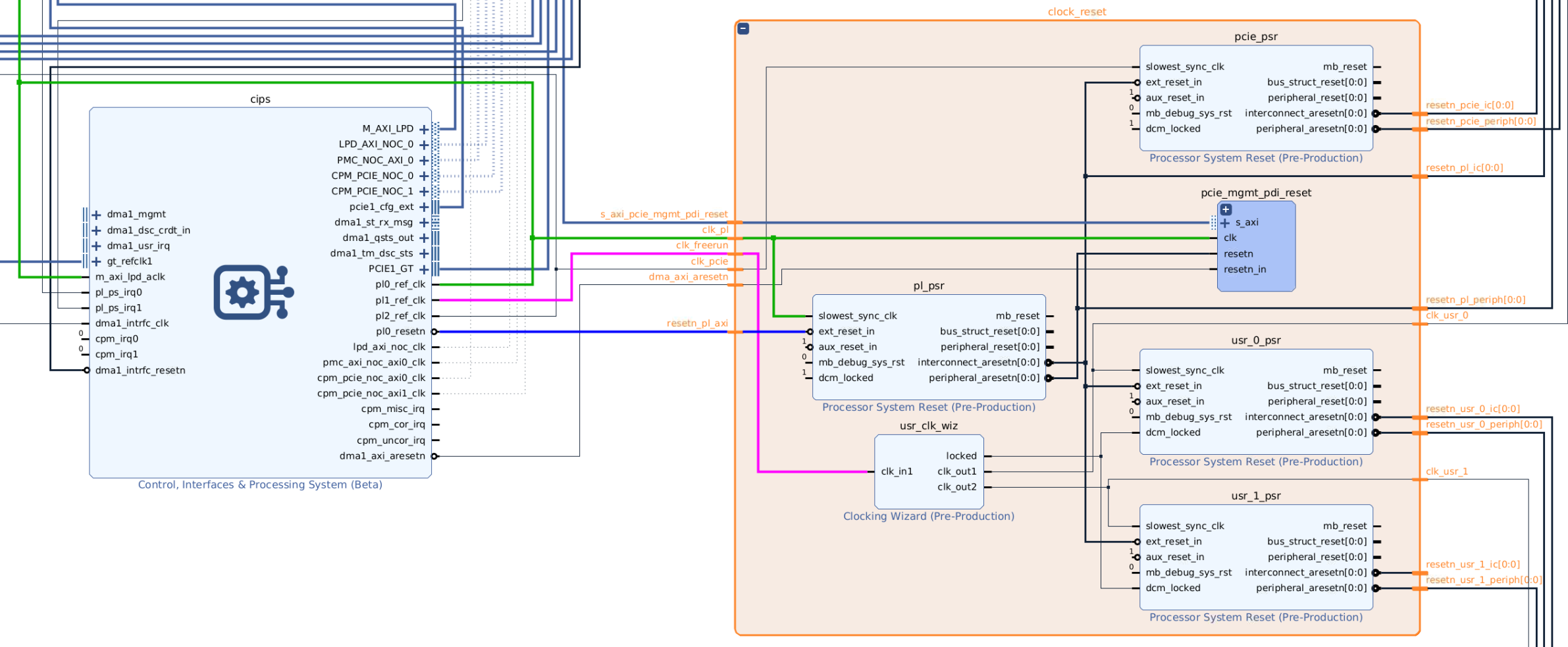

The AVED Clock Reset module is used to create kernel clocks and distribute synchronous resets throughout the device. The Clocking Wizard is used to create additional PL clocks, and the synchronous resets are generated using the Processor System Reset IP.

Sub-blocks¶

usr_clk_wiz¶

This IP uses the 33.333333MHz from the CIPS (pl1_ref_clk) to create the 399.99600MHz and 599.99400MHz clocks for user logic. The resets from usr_0_psr and usr_1_psr are asserted when the ‘locked’ signal from this module is asserted.

pl_psr - Programmable Logic Processor System Reset¶

This block synchronizes the CIPS reset (pl0_resetn), to the CIPS 100MHz clock (pl0_ref_clk). Then it is used to create device wide resets synchronous to the PCIe 250MHz clock and the clock wizard 399.99600MHz and 599.99400MHz clocks.

pcie_psr - PCIe Processor System Reset¶

This block creates a reset signal synchronous to the 249.999985MHz PCIe (dma interface) clock.

usr_0_psr - User0 Processor System Reset¶

Using the 100MHz synchronized reset output from pl_psr and the dcm_locked signal from the clock wizard, this block creates a reset signal synchronous to the clock wizard 399.99600MHz clock. This reset is used by xbtest, and it would also be used for user logic.

usr_1_psr - User1 Processor System Reset¶

Using the 100MHz synchronized reset output from pl_psr and the dcm_locked signal from the clock wizard, this block creates a reset signal synchronous to the clock wizard 599.99400MHz clock. This reset is used by xbtest, and it would also be used for user logic.

pcie_mgmt_pdi_reset¶

This block is reserved for future growth.

Flash Reload¶

AVED only supports a Power-On-Reset to reload a design from flash. It does not support a hot reset to reload the flash due to the system complexity of resets which are described below.

When PCIe Reset asserts, this reset does not naturally progress to the rest of the device.

The reset structure of Versal is not structured/tested in a way that it can be reset properly without reloading the entire design from flash (in the desired time frame).

The programmatic way to reset NOC, PS, DDR, HBM, etc is by issuing a POR and reloading the design from flash.

The device POR cannot be issued until the host has issued the PCIe reset sequence or adverse behavior on the host may be observed.

Some DELL servers reboot themselves if the PCIe link goes down unexpectedly.

Page Revision: v. 17