AVED Overview¶

Table of Contents¶

Introduction¶

This section contains an overview of the AMD Alveo™ Versal™ Example Design (AVED) for the Alveo V80 data center accelerator card. The AVED V80 provides a starting point for applications using the familiar Vivado design flow on production-ready Alveo PCIe cards. The AVED has the following design components:

The base hardware design for establishing PCIe® host connectivity and logic for common system management operations.

A small amount of demonstration application logic is also included but intended for removal and replacement with the user’s own application logic.

A firmware library running within the V80s RPU implements a management interface to a companion host operating system driver and utility application so that the basic features of the V80 card can be managed within the development and deployment systems.

A build flow script is also provided to demonstrate a full, end-to-end build process for both the base hardware design and software components described above.

Alveo V80¶

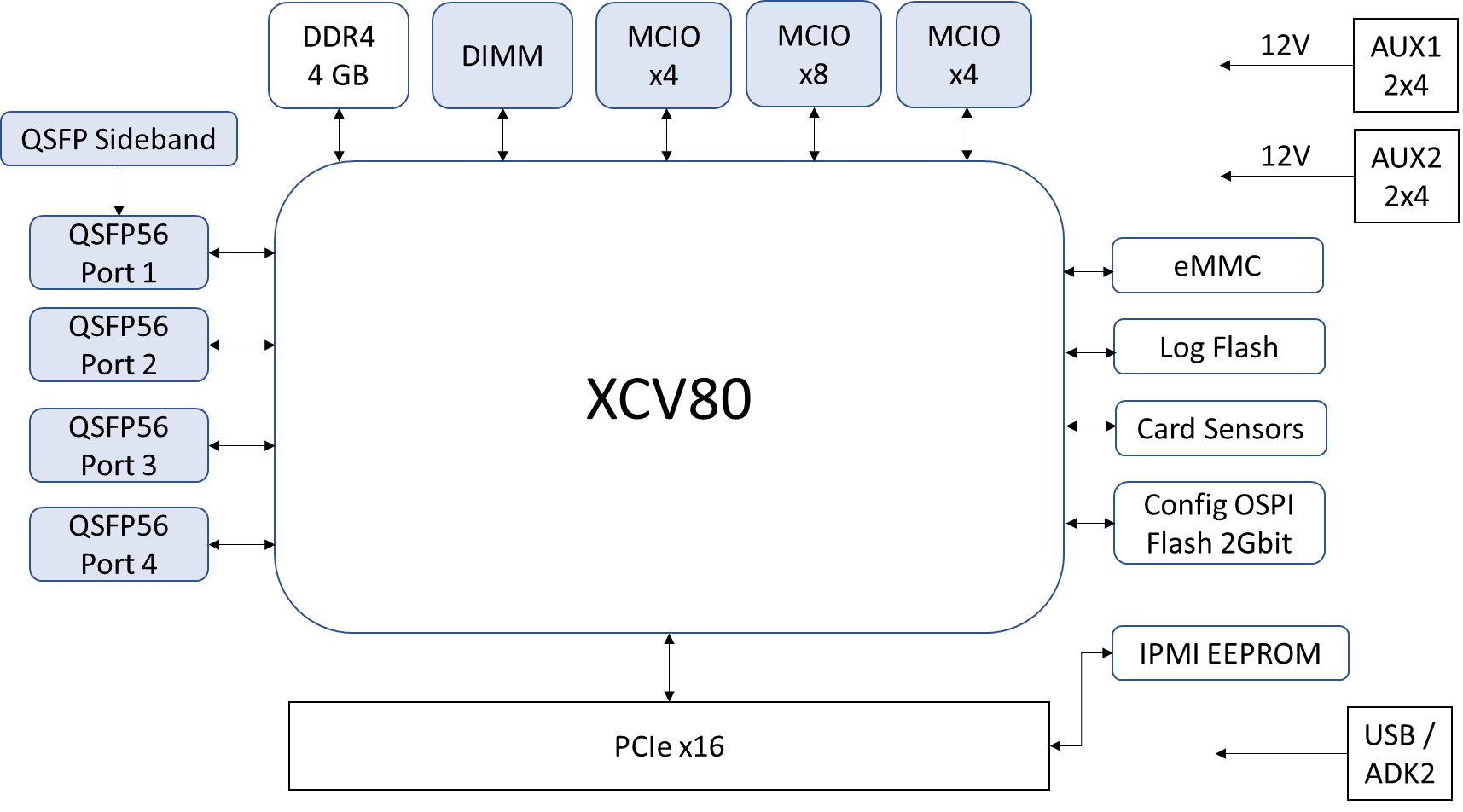

The Alveo V80 is a high performance data processing card in a PCIe form factor containing a Versal HBM FPGA device, DDR memory, and a variety of communication interfaces. The Alveo V80 has a broad range of market applications in high-performance compute, analytics, networking, storage, fintech, and blockchain. The following diagram provides a high level overview of the primary card features and interfaces. See the Alveo V80 Data Center Accelerator Card Data Sheet (DS1013) for information on the card and its capabilities.

Alveo Versal Example Design¶

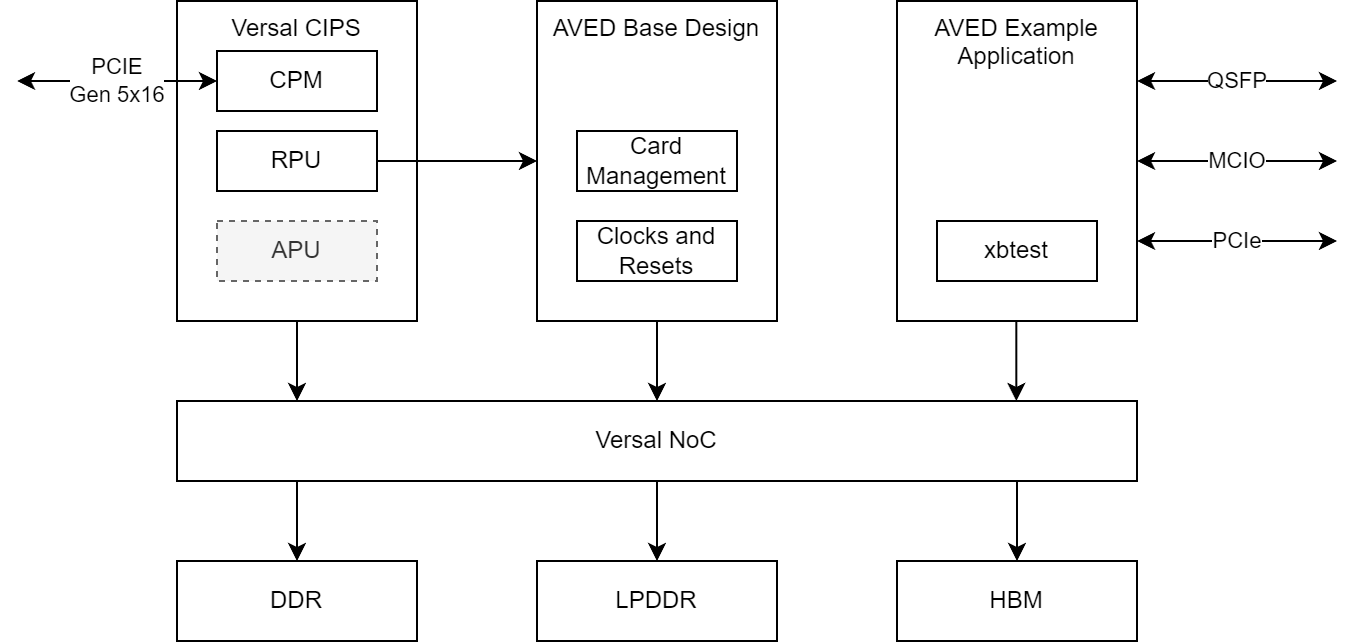

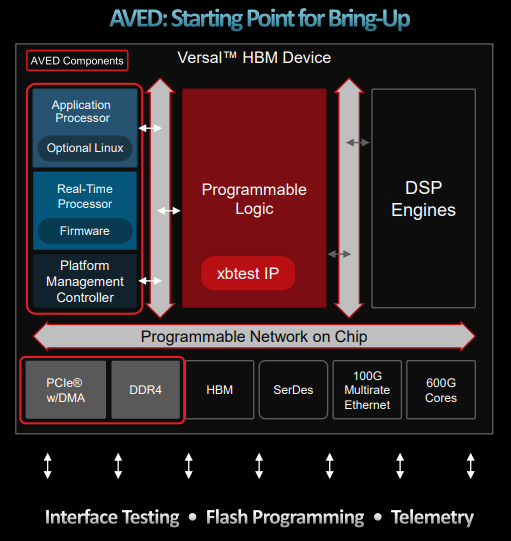

The AVED provides a robust starting point for application designers who wish to build and rapidly deploy solutions on Alveo V80 hardware. To support a broad range of markets, the AVED is delivered as a Vivado centric design with a well documented design architecture. The combination of the AVED base hardware design and companion software layers embodies Alveo’s best practice solutions to common application functions such as card management, device programming, and host to card data exchange. The following diagram shows an overview of the AVED in the context of the Alveo V80 FPGA resources.

Some notable characteristics of the AVED V80 include:

The AVED’s base design logic has been simplified to focus on the common set of card and application management functions, which increases the amount of available device resources for the user’s application.

The AVED is built on a Vivado centric design flow so that the application developer can leverage all of the available design optimizations in the Vivado software and IP libraries in their applications.

The AVED’s design flow produces full programming images for the FPGA, which simplifies the overall design flow and avoids other management overheads associated with dynamic function exchange.

The AVED’s firmware provides a reference implementation of card management functions for both in-band (PCIe) and out-of-band (SMBUS/BMC) sensor access and card control, plus other application-level card management functions. This includes writing new PDIs into the card’s configuration storage device and then loading those PDIs onto the V80 FPGA.

NOTE: SMBus IP is NOT yet available in the hardware design.

AVED Hardware Architecture¶

The base design included with the AVED shows how the Alveo™ V80 card would operate with an example design. The key features of the base design’s hardware architecture are:

Reference configuration of the Versal™ CIPS for PCIe® and PS to allow connectivity to the V80 card and enablement of processing domains and associated PS peripherals that will be supported in the AVED firmware.

The Versal NoC is pre-configured to support the traffic requirements of the AVED base design.

The base design logic contains the necessary PL IP instances to access card telemetry and transfer of device programming information from the PCIe host to the card.

In the future, programmable logic based SMBus IP infrastructure would enable a remote management interface (RMI) to standard server management software.

An example application is provided to demonstrate access to the main memory interfaces of the Alveo V80 card. A minimum design that contains the AVED base logic can also be generated to serve as a starting point for user applications.

AVED Software Architecture¶

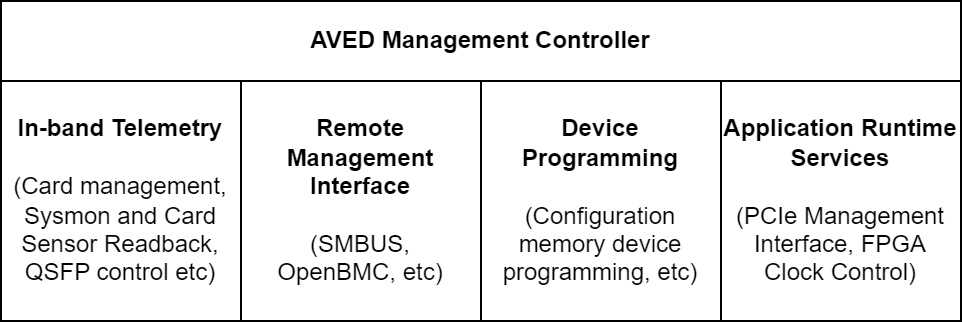

The AVED management controller (AMC) is reference firmware targeted to run on the V80 card’s RPU processors. There are four major groups of functionality provided in this reference firmware implementation:

Monitoring of card sensor state and other low level card control behaviors are provided in the form of an in-band (PCIe®) telemetry interface.

A remote management interface that is built on standard communication protocols (SMBus) to interface and service requests from well known server management software infrastructure, such as OpenBMC.

NOTE: SMBus IP is NOT yet available in the hardware design.

To support application development and later deployment, AMC also provides services to program and inspect the V80 card’s configuration storage memory.

A companion application (ami_tool) allows access to application runtime services (for example clock management) to cards with AVED-derived designs in the system via the PCIe host driver provided as part of the AVED Management Interface (AMI).

AVED Design Flow¶

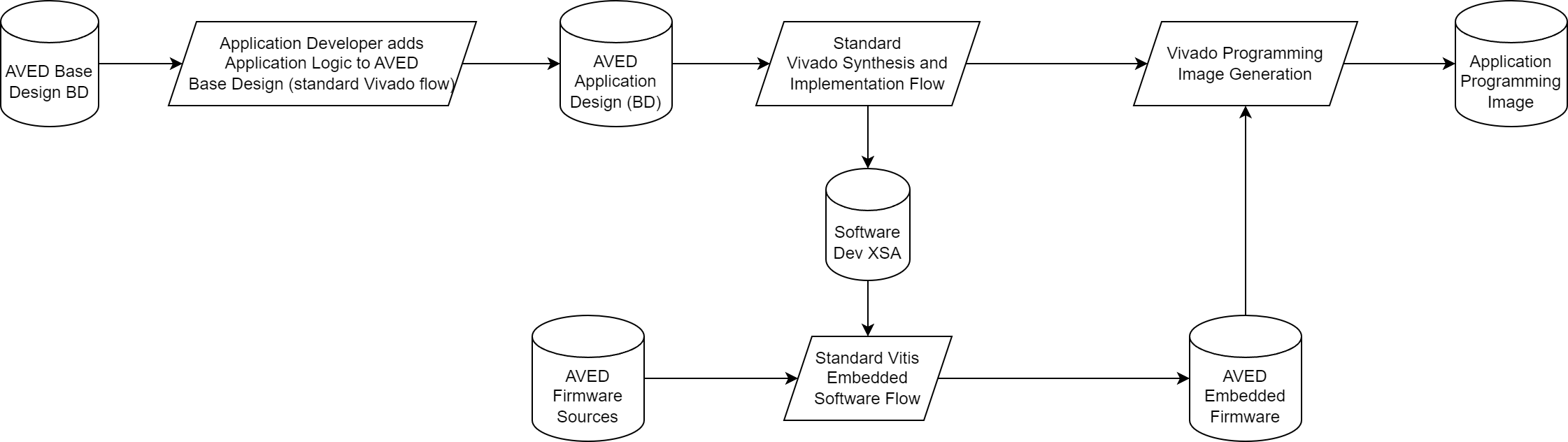

As a Vivado™-centric design, the AVED is built on the same standard design flows that are well known to the broad community of Vivado and Versal™ application developers. Because AVED includes a hardware base design and firmware images, AVED’s design’s source files are delivered in a particular source directory structure. A utility script is provided to encapsulate the complete build flow from end to end.

The diagram above shows a high level overview of the AVED build process. Notable aspects of the build process are:

Use of familiar Vivado design steps (capture of design in IP integrator, synthesis and implementation) for generation of the application programming image.

AVED base design BD reused as the starting point for the application design BD.

Use of Vitis™ embedded software flow to compile AVED firmware image for inclusion into final programming image.

Page Revision: v. 34