AVED V80/V80P - Hierarchy Overview¶

Introduction¶

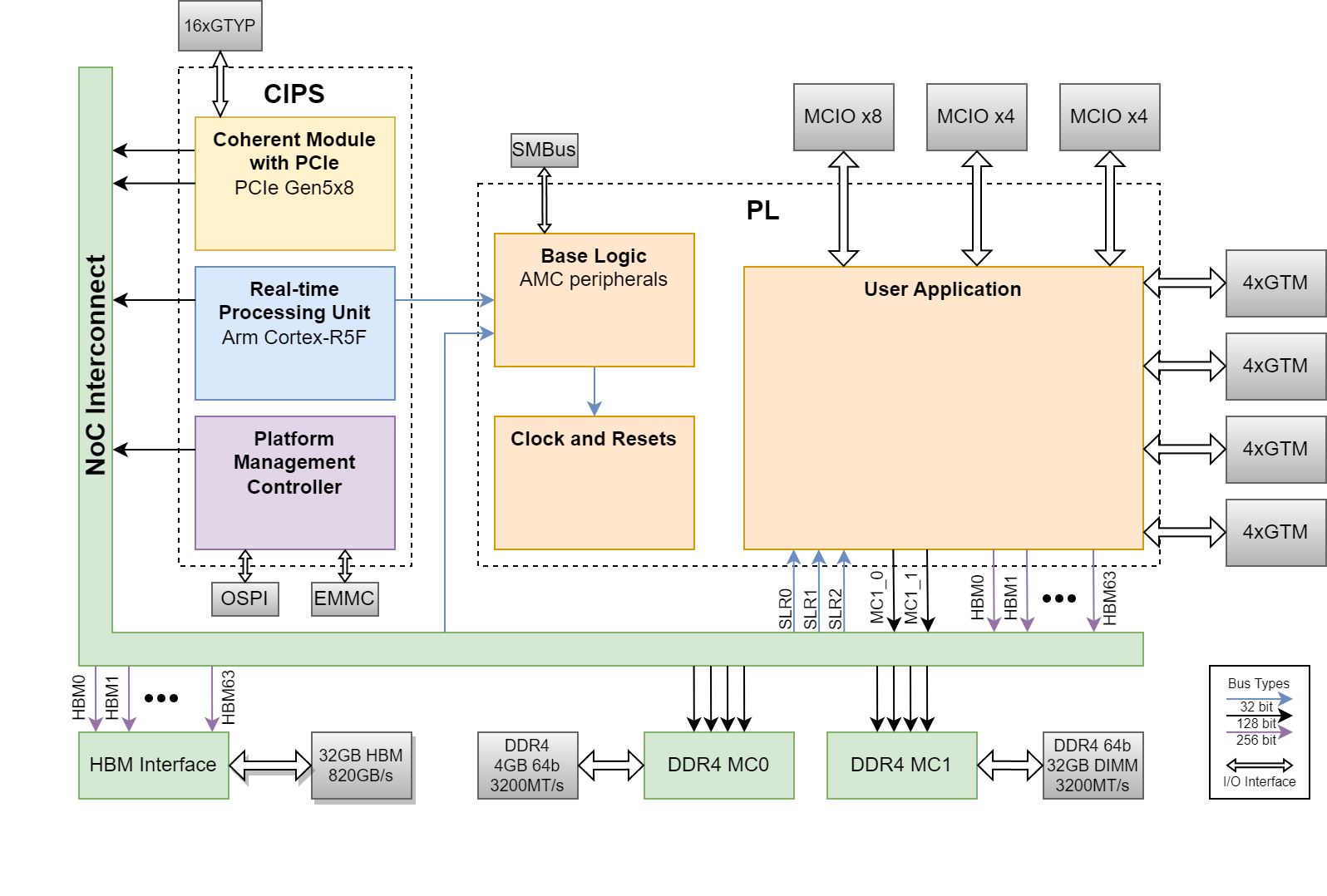

The AVED design is a PCIe® based design that is used to demonstrate the capabilities of the card, firmware, and drivers. The design is composed of 4 major blocks: CIPS, Base Logic, Clocks and Resets, and User Application. The NoC interconnect is used to route AXI traffic across the device.

Block Diagram¶

The following is the block diagram of the design.

Control, Interfaces and Processing System¶

The Control, interfaces, and processing system (CIPS) IP configures the various hard blocks that are present in the AMD Versal™ device. The AVED design configures the coherent module with PCIe (CPM) block, the real-time processing unit (RPU) block, and the platform management controller (PMC) block through the CIPS IP. The primary blocks used in this design are summarized in the following table.

| Block | AVED Usage | More information |

|---|---|---|

| Coherent Module with PCIe | The CPM block contains the PCIe gen5x8 and QDMA hardened IPs on the device. It interfaces between the PCIe transceivers and the NoC interconnect to allow communication from the PCIe host to the device. It is configured with the minimum necessary to demonstrate functionality of the card. | Versal CPM CCIX Architecture Manual - Introduction to CPM |

| Real-time Processing Unit | The RPU block contains the R5 processor that is used for running the AMC firmware on the device. This is part of the processing system low-power domain (PS LPD). The primary purpose of this block in this design is to handle the board management functions of the card. | Versal TRM - LPD Architecture |

| Platform Management Controller | The PMC block contains a MicroBlaze-based processor subsystem. It is primarily responsible for managing the bootup, configuration, and internal monitoring of the device. It interfaces with the external flash devices to read/write device images for device configuration. This compulsory unit is required for the Versal device to function. | Versal TRM - PMC Architecture |

Programmable Logic (PL)¶

The PL region contains the soft logic IP and I/O connections. It is separated into 3 main blocks: Base Logic, Clocks and Resets, and User Application. It contains I/O connections to the SMBus, MCIOs, and QSFP I/O interfaces. A summary of the function of each block is described in the table below. Note: The V80P does not have MCIO or QSFP interfaces; all MCIO and QSFP logic described in the PL is for V80 only.

| Block | AVED Usage | More information |

|---|---|---|

| Base Logic | The base logic region primarily contains peripheral IPs that are used by the R5 processor to handle the card and driver management firmware. This includes the SMBus IP, command queues, and identification ROMs.

| AVED V80/V80P - Base Logic |

| Clocks and Resets | The clock and resets region contains the clocking wizards and reset synchronizer blocks for the user application. It also contains the logic to facilitate hot-reset/PDI reload of the device. | AVED V80/V80P - Clock Reset Module |

| User Application | The user application contains xbtest IPs and accompanying logic to exercise the various I/Os on the device. It connects to MCIO and QSFP interfaces directly and additionally to the NoC. Through the NoC, it interfaces with the PCIe, HBM, and DDR4 blocks. This block is meant to be replaced with custom logic and IP. | xbtest User Guide |

NoC Interconnect¶

The NoC interconnect facilitates high bandwidth transport between the various CIPS blocks, the PL, and the DDR4 and HBM memories. Through the NOC IP configurator, the HBM and DDR memory controllers are configured and instantiated into the design. The V80 and V80P both contain 32GB of internal HBM and 4GB DDR4. Additionally, the V80 also includes a 32GB DDR4 DIMM. In the AVED, the 4GB of DDR4 is allocated to the R5 processor and DMA over PCIe. The 32GB HBM and (for V80 only) the 32GB of DDR4 is available for the user application.

Page Revision: v. 32