UL3524 Ultra Low Latency Trading |

FINN on UL3524¶

Description¶

This reference design demonstrates the latency of a data stream through a FINN IP block on the UL3524.

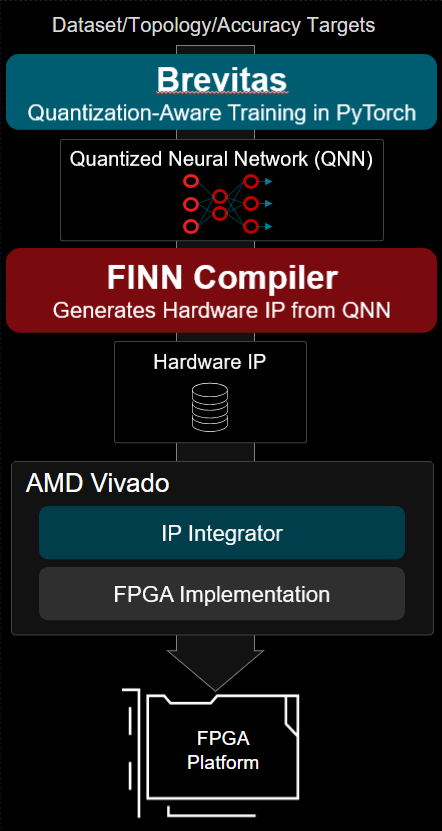

The FINN compiler is an open source tool that generates Quantized Neural Network (QNN) Hardware IP blocks targeting AMD FPGAs.

q3

The QNNs are generated by Brevitas based on PyTorch network descriptions.

The output of FINN is in the form of a “Stitched IP” block, which can be integrated into a custom FPGA design with Vivado™ IP Integrator.

This design is not a complete solution, but rather a demonstration of how the FINN tool can be used to generate a FINN IP block targeting the UL3524 board.

As a starting point, the well documented Cybersecurity-mlp example is modified to target the UL3524. In addition, the Cybersecurity-mlp configuration is modified to minimize data latency through the block.

Building the Design¶

For General instructions refer to this link Design Creation

The setup.tcl file for FINN_Latency in particular runs extra steps including synthesis and implementation. This is necessary because there are constraint conflicts that must be removed or critical warnings are reported. The details can be observed in the setup.tcl file found here FINN Latency setup.tcl

Sections¶

The following links provide additional design details, including simulation and HW Manager support.

Support¶

For additional documentation, please refer to the UL3524 product page and the UL3524 Lounge.

For support, contact your FAE or refer to support resources at: https://support.xilinx.com

Copyright © 2020–2023 Advanced Micro Devices, Inc